基于FPGA的TS over IP的設計與實現

2.4.2 FPGA與MCU通信的實現

本文引用地址:http://www.104case.com/article/279225.htm此模塊實現FPGA與MCU之間的通信,在本設計中主要采用的是EMIF接口的方式,與此同時我們還使用了MCU的通用I/O口,采用了以EMIF接口為主、通用I/O口為輔的混合通信方式,使FPGA與MCU之間的通信更加地靈活,邏輯框圖如圖4所示。

在本系統中R8051XC2提供了EMIF接口來訪問外部的數據或程序存儲器,該接口具有23bit的數據總線“memaddr”,可以訪問最大16MB的存儲空間;8bit的輸出數據總線“memdatao”和8bit的輸入數據總線“memdatai”,讀寫控制信號“memwr”和“memrd”,以及一個響應信號“memack”。

R8051XC2為EMIF接口提供了基于三個輸入信號的等待狀態,三種信號分別為:“mempsack”主要用于外部程序存儲器;“memack”主要用于外部數據存儲器;“sfrack”主要用于外部特殊功能寄存器。這些管腳的狀態在傳輸指令或數據時被采樣,例如,在使用“memrd”和“memwr”對外部的數據存儲器進行讀寫操作時,處理器會對“memack”進行采樣來確認外部存儲器是否已經完成操作。還提供了一個全局等待信號“waitstate”,表示插入一個等待狀態,無論是由什么原因引起的。

控制內部產生的程序或外部數據存儲器的等待狀態長度的寄存器是“ckcon”,它的值作為初始值裝入內部等待狀態的計數器中。當有一個外部數據存儲器的訪問初始化時,ckcon[2:0]的值被裝入內部等待狀態計數器,這個計數器會強制將waitstate信號置1,使處理器中的寄存器和觸發器進入等待狀態,直到計數器的值減少到0。

本文設計的系統在兩個不同的層次中包含兩個時鐘域,需要使用兩個PLL模塊來實現,其中一個在FPGA的頂層模塊中為MAC模塊和MCU接口模塊提供100MHz與80MHz的時鐘,并通過locked接口產生低有效的復位信號。另一個PLL模塊為FPGA提供運行時所需的時鐘信號。

2.4.3 異步時鐘域通信的實現

在本文介紹的系統中,存在著兩個時鐘域,其中TS模塊工作在標準中要求的27MHz的時鐘域中,處理器和MAC模塊工作在100MHz的時鐘域中,其中TS模塊需要和處理器之間進行數據傳輸。在傳輸中需要進行異步時鐘域處理的主要包括兩種信號:一種是控制信號,另一種是數據信號。在異步時鐘域的通信中需要解決兩個問題:一是信號的同步,二是盡量減少亞穩態的影響。

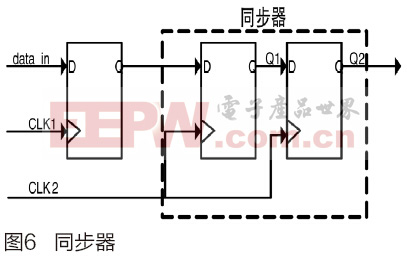

對于第一個問題,在本文中使用部分握手協議來進行信號的同步[7]。部分握手協議的過程中,兩個通信的時鐘域不需要完全了解對方的狀態,可以按順序發送或撤銷各自的握手信號。由于雙方不需要等待對方的回應,就可以撤銷自己的信號并繼續執行協議,因此相對于完全握手協議,部分握手協議的穩定性稍差,當然可以使用更少的時間完成一次握手傳輸。根據使用的信號不同,部分握手協議又可以分為兩種。第一種為使用電平和脈沖的同步握手信號。第二種為使用脈沖的同步握手信號。在此本文使用脈沖的同步握手信號,其過程如圖6所示[6]。

在這種握手機制中采用脈沖同步器接收通信雙方的握手信號,如果時鐘域A的時鐘頻率比時鐘域B的時鐘頻率快兩倍時,可以采用邊沿同步器來收握手信號。從圖6中可以看出,這種握手機制中,時鐘域A需要2個時鐘周期,時鐘域B需要3個時鐘周期,所耗費的時鐘周期最少。

握手機制的優點是可以在時鐘頻率相差較大的時鐘域之間進行通信,可以進行多位傳輸。缺點是需要額外的多個時鐘周期完成握手的流程,降低了系統的效率。

對于亞穩態的減少,使用常用的同步電路的方法來處理,同步電路的原理是降低出現亞穩態的概率,由圖6中可分析出,第一個時鐘域的信號到達第二個時鐘域的第一個觸發器時,很可能無法滿足建立和保持時間,從而導致在觸發器的輸出端出現亞穩態,當這種狀態持續不到一個周期時,可以通過增加一級觸發器來消除該亞穩態,這樣第二個觸發器的輸出信號就可以滿足同步信號的要求,可以達到異步電路同步化的效果[4]。

3 系統狀態機及各狀態說明

下面主要對執行TS over IP操作時系統的狀態轉換情況進行說明。系統狀態轉換圖如7所示。

信號說明:

wdata1,wdata2 :RAM1和RAM2的可寫數據信號。

wchk1,wchk2 :RAM1和RAM2的可寫包頭信息信號。

rdata1,rdata2 :RAM1和RAM2的可讀信號。

狀態圖說明,除開始和結束狀態外,本系統共包含六個狀態:

tcp/ip相關文章:tcp/ip是什么

評論