基于FPGA的TS over IP的設計與實現

摘要:隨著互聯網的發展, 數字電視信號的網絡傳輸得到了越來越多的關注,本文設計與實現了一種基于FPGA和MCU(R8051XC2)的TS over IP系統,并對傳統的TS over IP系統進行了改進。此系統通過從標準TS流接口接收TS流,將其以乒乓操作的方式存放在兩個雙口RAM中,再通過一定方法封裝IP包發送至網絡,實現了TS流和網絡IP數據包的相互轉換。通過向系統推送TS流數據并使用抓包軟件對經過系統的數據進行分析統計的方法證明,得出以下結論,此系統在相同情況與有限的硬件條件下,相比傳統的使用FIFO作為緩沖器的系統,系統運行效率有了明顯的提高。

本文引用地址:http://www.104case.com/article/279225.htm引言

隨著互聯網的發展,人類進入了網絡化、數字化的時代。在三網融合的政策背景下,數字電視信號的網絡傳輸得到了越來越多的關注。與此同時,先進的嵌入式技術也對數字媒體的發展起到了推動的作用。TS流是根據ITU-T Rec.H.222.0|ISO/IEC 13818-2 和ISO/IEC 13818-3協議而定義的一種數據流,主要用來傳輸數字電視的視頻節目、音頻節目和一些用戶信息,它是以包的方式存在,一個TS包一般為188或204字節,其廣泛用于電視信號的傳輸中。當前的廣播電視傳輸主要是TS流在現有的有線電視網絡中進行傳輸。而本文的TS over IP技術是將TS流數據包轉換成IP數據包,并能夠在網絡中進行傳輸。使只有網絡接口的終端設備可以接收到電視信號[1]。

目前實現該技術的主要方法是通過MCU IP核在FPGA中模擬出一個控制器來控制其余的子模塊實現[2]。本文設計的系統使用FPGA芯片和MCU芯片,兩個芯片之間通過EMIF接口進行通信,并使用兩個雙口RAM,以及DMA的方式來實現系統。

1 系統概述及流程

1.1 系統概述

本系統實現了將從TS傳輸設備中接收到的TS流數據轉換為IP數據包,并使其能在網絡中傳輸。本系統基于FPGA實現,由一個MCU進行控制,可以通過設置初始時的IP和MAC地址將數據發送到不同的目的主機。

目前類似的系統大都使用現成的FIFO來對TS數據進行暫時的存儲并通過現成的TCP/IP協議代碼來封裝IP包。在使用傳統的方法時,當FPGA性能不夠時會導致丟包的現象出現。而FPGA與MCU在通過FIFO進行通信交換數據與MCU的處理速度過低與數據的多次交換是導致這一現象的主要原因。所以為了提高系統的運行效率,使系統能夠在數據量非常大的情況下或者FPGA性能不是很好的情況下仍能夠正常運行,本系統采用了兩個雙口RAM通過乒乓操作來完成TS數據的暫時存儲,并通過程序在RAM中寫入數據來實現IP包的封裝,封裝完成后通過DMA的方式將數據傳輸到MAC模塊中進行發送的設計,避免了FPGA與MCU進行數據交換與運行復雜的TCP/IP封裝程序的過程,從而提高系統的運行效率。

本系統使用了FPGA+MCU進行實現,由于兩塊芯片的時鐘頻率不同,則系統涉及到了跨時鐘域通信問題以及數據的亞穩態問題,所以本系統使用了應答機制以及同步電路來避免異步時鐘域通信帶來的問題。

1.2 系統流程

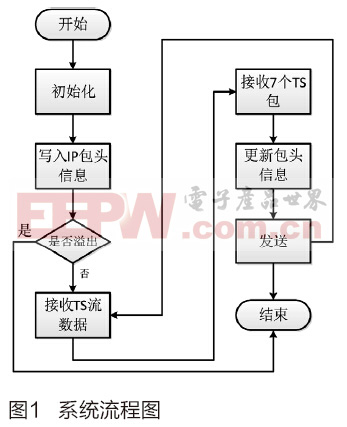

如圖1所示,系統流程由3個部分組成。首先,在程序啟動后,由MCU來對整個系統進行初始化配置,為之后系統的運行做好準備。接著MCU通知FPGA初始化完成,開始接收TS數據,并將這些數據儲存在RAM中,當接收7個TS包以后,程序會檢測是否由于傳輸數據過快出現數據溢出。完成溢出檢測后,系統會對RAM中的IP包頭信息進行更新,信息更新完成之后的IP包會以DMA的方式傳輸到MAC中并最后由MAC模塊發送到網絡之中。

2 系統模塊概述

2.1 系統總體結構

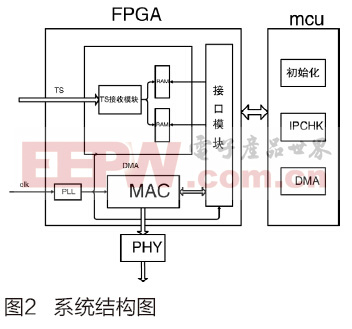

該系統主要由TS接收模塊、IP包封裝模塊、IPCHK模塊、DMA模塊、EMIF接口等模塊組成。通過這些模塊我們實現了TS流的接收、網絡傳輸協議以及系統內各模塊通信等功能。系統結構圖如圖2所示。

其中,TS接收模塊、MAC模塊以及接口模塊由FPGA實現。IP包封裝模塊、片選模塊、IPCHK模塊以及DMA控制模塊在MCU中實現。

2.2 TS流接收的實現

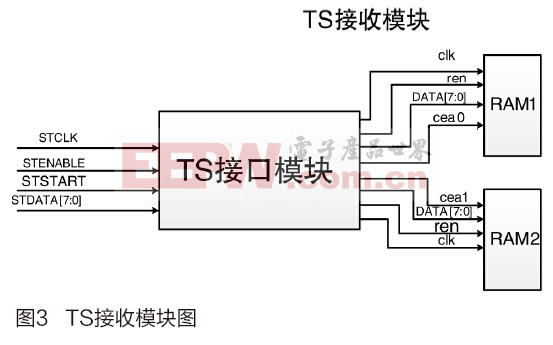

系統中設計的TS接收模塊可以直接與TS流的編碼器相連接,其基本結構如圖3所示。

本模塊的時鐘來自于編碼器,接收符合時序的SPI形式的TS流數據。接收模塊接收數據后將數據存儲到RAM之中。如圖3所示,本模塊使用了兩個RAM進行存儲與分裝IP包,并使用乒乓操作對兩個RAM進行控制,在雙RAM乒乓操作的模式下,系統可以在處理前一批數據的同時繼續接收數據,從而提高系統的運行速度,防止數據溢出[8]。同時由于本設計使用UDP協議發送TS包,每個TS數據包的長度為188字節,而IP包的最大長度為1500字節,RAM 0~41的空間用來存放IP包頭數據,所以TS數據從第43個地址開始存放,直到接收到7個TS包即到地址1357后切換另一個RAM。在一個RAM存滿之后,接收模塊會通過標志位通知MCU進行接下來的工作。

2.3 網絡協議的實現

2.3.1 IP包封裝模塊

IP包封裝模塊即網絡協議的實現模塊是在開機時運行,主要負責對MAC模塊進行初始化配置與設置初始的IP地址和MAC地址。由于為了節省FPGA與MCU數據交換以及運行TCP/IP程序的開銷,本系統將IP包的封裝是由MCU直接對RAM寫入數據來完成的,根據TCP/IP協議的規定,IP包封裝模塊將已經設置好的IP包頭數據分別寫入兩個RAM地址的0~41之中,將其作為IP包的包頭信息。完成IP包的包頭信息寫入之后,本模塊通過置位標志位通知TS接收模塊開始工作。

2.3.2 IPCHK模塊

IPCHK模塊實現了IP包頭的更新功能,本模塊是在MCU接到RAM滿的信號后進行調用。為了省去運行復雜的TCP/IP程序所用的時間,需要手動完成對IP包包頭更新以及校驗和的計算。首先IPCHK模塊會對IPID進行刷新,之后對IPID更新后的IP包的校驗和進行重新計算,并在計算完成之后將新的IPID檢驗和寫入RAM的12、13、18、19號地址 之中,最后通知系統準備調用DMA模塊。

2.3.3 MAC模塊

本系統中,MAC模塊通過MCU接口模塊與MCU芯片進行通信,并由MCU進行初始化,初始化完成后對PHY芯片進行配置,將接收到的含有TS數據的IP包發送給PHY芯片,進而傳輸到網絡中。由于基于FPGA的MAC IP core已經非常成熟,這里不再贅述。

2.4 系統各模塊間的通信

2.4.1 DMA控制模塊

本系統中PHY芯片與FPGA的數據交換是用過DMA來實現的,DMA模塊是在IPCHK完成后進行調用。此時,DMA模塊根據FPGA返回的RAM片選控制信息,以DMA的方式將RAM中的數據傳輸到MAC中。DMA模塊使得MCU可以從數據搬用的工作中解脫出來,從而提高了程序運行的效率,防止了數據的溢出。

tcp/ip相關文章:tcp/ip是什么

評論