神級經(jīng)典設(shè)計案例:用ARM和FPGA搭建神經(jīng)網(wǎng)絡(luò)處理器通信方案

2.2硬件連接

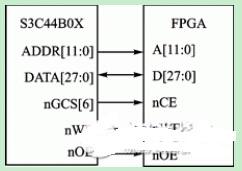

本文引用地址:http://www.104case.com/article/279151.htm從上面的介紹容易發(fā)現(xiàn),ARM芯片的通信對象是基于SRAM工藝的FPGA芯片上的存儲體。因此,FPGA芯片作為存儲設(shè)備時,ARM芯片可直接與其相連。ARM與FPGA硬件連接示意圖如圖6所示。

圖6 ARM與FPGA硬件連接示意圖

ARM與FPGA的片上存儲體的地址總線連接設(shè)置為12位,足夠存儲和尋址需求。

數(shù)據(jù)總線的寬度為28位。神經(jīng)網(wǎng)絡(luò)處理器的數(shù)據(jù)精度為16位[4],F(xiàn)PGA樣本數(shù)據(jù)寄存器還有12位外部擴展存儲器的地址數(shù)據(jù),因此整個數(shù)據(jù)總線的寬度為二者之和。除樣本數(shù)據(jù)寄存器之外的片上存儲體,數(shù)據(jù)線占用28位數(shù)據(jù)總線中的低16位。

控制總線包括ARM端的片選線nGCS6和讀/寫控制線。對ARM相應的寄存器進行配置可激活BANK6(FPGA片上存儲體)和讀/寫數(shù)據(jù)。

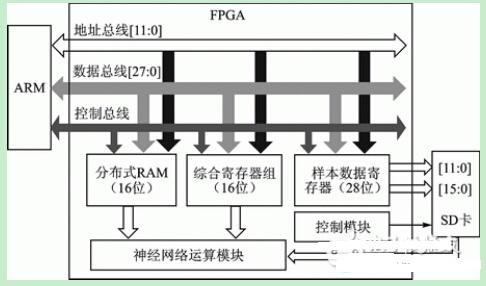

根據(jù)數(shù)據(jù)存儲位置的不同,硬件連接可分成兩方面。如圖7所示。

圖7 FPGA端部分硬件連接示意圖

3 ZDMA控制設(shè)計

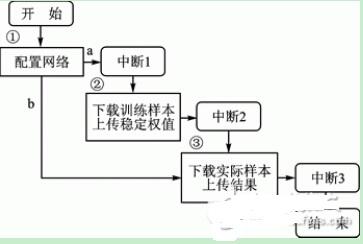

ARM端與FPGA端的數(shù)據(jù)通信如圖8所示,分為3個階段:

①網(wǎng)絡(luò)初始化階段的數(shù)據(jù)通信:配置網(wǎng)絡(luò)初始化數(shù)據(jù)。a)需對網(wǎng)絡(luò)訓練執(zhí)行階段②,b)否則執(zhí)行階段③。

②網(wǎng)絡(luò)訓練階段的通信:下載訓練樣本數(shù)據(jù),訓練完成上傳穩(wěn)定的權(quán)值。

③實際應用階段的通信:下載實際樣本數(shù)據(jù),上傳處理結(jié)果。

每一個階段都是在ZDMA的方式下進行。每一個階段完成后都會進入中斷,提示本階段完成并進行下一步操作。

圖8 數(shù)據(jù)通信階段流程圖

3.1下載數(shù)據(jù)時ZDMA的配置

按照是否為樣本數(shù)據(jù),通信可分為兩個階段:一是面向FPGA片上集成存儲系統(tǒng)的非樣本數(shù)據(jù)通信,二是面向FPGA片外擴展存儲器的樣本數(shù)據(jù)通信。

本設(shè)計使用ZDMA0、ZDMA1兩個通道中的一個。與ZDMA有關(guān)的特殊功能寄存器有:

ZDMA控制寄存器(①ZDCONn):主要用于對DMA通道進行控制,允許外部DMA請求(nXDREQ)。

ZDMA0/1初始源/目的地址和計數(shù)寄存器、ZDMA0/1當前源/目的地址和計數(shù)寄存器。

ZDMAn初始/當前源地址寄存器(②ZDISRC、③ZDCSRC):初始源地址為數(shù)據(jù)在ARM芯片內(nèi)存的存放地址;當前源地址為即將傳輸?shù)臄?shù)據(jù)的內(nèi)存地址,值為初始源地址+計數(shù)值。

ZDMAn初始/當前目的地址寄存器(④ZDIDES、⑤ZDCDES):分為兩個階段:第一階段傳輸非樣本數(shù)據(jù)時初始目的地址為BANK6的起始地址;當前目的地址是變化的,為初始目的地址+計數(shù)值。第二階段傳輸樣本數(shù)據(jù)時初始目的地址也是當前目的地址,為樣本數(shù)據(jù)寄存器的地址。

ZDMAn初始/當前目的計數(shù)寄存器(⑥ZDICNT、⑦ZDCCNT):初始值為0,當前值隨著傳輸數(shù)據(jù)的個數(shù)逐一遞增,直至達到所有數(shù)據(jù)的數(shù)量。樣本數(shù)據(jù)和非樣本數(shù)據(jù)的傳輸分兩個階段進行,各自獨立。

從這個過程中可以看出,配置ZDMA時需考慮FPGA端存儲結(jié)構(gòu)體多樣性的問題。

3.2上傳數(shù)據(jù)時ZDMA的配置

神經(jīng)網(wǎng)絡(luò)處理器的穩(wěn)定權(quán)值和處理結(jié)果存儲在FPGA上統(tǒng)一編址的專用寄存器組B中,不存在存儲結(jié)構(gòu)體多樣性的問題,所以上傳數(shù)據(jù)時ZDMA的配置相對簡單:

初始源地址即專用寄存器組B的起始地址,每傳送一次數(shù)據(jù)專用寄存器組的地址指針+1并作為當前源地址。

初始目的地址為要存放數(shù)據(jù)的內(nèi)存塊的起始地址,每傳送一次數(shù)據(jù)內(nèi)存塊地址指針+1并作為當前目的地址。

計數(shù)寄存器的初始值為0,每傳送一次數(shù)據(jù)其值+1,達到設(shè)定的目標值時數(shù)據(jù)上傳即完成。

結(jié)語

本文首先介紹了人工神經(jīng)網(wǎng)絡(luò)的模型和算法以及FPGA的實現(xiàn),并通過對網(wǎng)絡(luò)結(jié)構(gòu)的分析設(shè)計了FPGA端的數(shù)據(jù)存儲系統(tǒng)。然后分析了ARM端和FPGA端各自的功能,在此基礎(chǔ)上把兩者結(jié)合在一起,設(shè)計了一種利用ARM的ZDMA方式相互通信的方案。

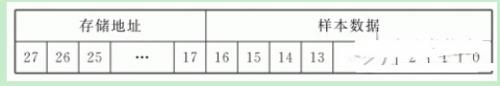

第一,存儲位置為FPGA端的外部擴展存儲器。①ARM與FPGA通過12位地址總線、28位數(shù)據(jù)總線及控制總線直接相連,數(shù)據(jù)寫入樣本數(shù)據(jù)寄存器。②樣本數(shù)據(jù)寄存器的28位數(shù)據(jù)按照12位地址數(shù)據(jù)、16位樣本數(shù)據(jù),通過FPGA與外部擴展存儲器之間的12位地址總線、16位數(shù)據(jù)總線,在存儲控制模塊的控制下,把樣本數(shù)據(jù)寫入擴展存儲器。因此,把樣本數(shù)據(jù)寄存器分為兩部分,低16位為樣本數(shù)據(jù),高12位為該樣本數(shù)據(jù)在外部擴展存儲器的存儲地址,如下所示。

第二,存儲位置為FPGA的片上存儲體。ARM與FPGA通過12位地址總線、28位數(shù)據(jù)總線中的低16位、控制總線直接相連,控制寄存器組、專用寄存器組、分布式存儲器連接在這些總線上面。

片上集成存儲系統(tǒng)采用統(tǒng)一編址的方式,其優(yōu)勢在于可以通過ARM芯片的DMA方式進行數(shù)據(jù)傳輸,既可以提高傳輸速率又能夠釋放CPU.外部擴展存儲器因為只受FPGA控制而采用獨立編址,但地址域的設(shè)計接續(xù)片上集成存儲系統(tǒng)的地址,如此方便操作。

fpga相關(guān)文章:fpga是什么

通信相關(guān)文章:通信原理

存儲器相關(guān)文章:存儲器原理

評論