TMS320C6678存儲器訪問性能 (下)

由于總共有10 個EDMA TC,而只有8 個DSP 核,在這些測試里,8 個TC 在SL2 和8 個核的LL2 之間傳輸數據,另兩個TC 則在SL2 和DDR 之間傳輸數據。

本文引用地址:http://www.104case.com/article/276393.htm盡管SL2 本身的帶寬非常高,但所有EDMA 訪問SL2 時都需要經過內部總線交換網絡的一個相同的端口,這個端口就成了這種情況下的瓶頸。這個端口的理論帶寬是500MHz x 32 bytes = 16000MB/s。如果所有EDMA 傳輸的優先級相同,帶寬會在這些傳輸之間平均分配。而當優先級不同時(上表中第二列是每個主模塊的優先級),優先級低的EDMA 傳輸得到的帶寬比較小。對負載很高的情況下,一些低優先級的傳輸可能會被“餓死”,也就是說,得到的帶寬為0。

根據Table 6中列出的不同EDMA TC 的區別,EDMACC1 TC1 和TC3,EDMACC2 TC1 和TC2在某些情況下獲得的帶寬會比其它TC 小,即使優先級相同。

2.2 多個主模塊共享DDR 的性能

多個主模塊同時訪問DDR 時,DDR 控制器會根據主模塊的優先級進行仲裁。

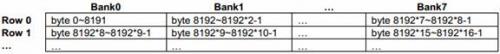

C6678 的DDR 控制器支持包含1,2,4,或8 個banks 的DDR 存儲器。現在大多數DDR3 存儲器都包含8 個bank,以C6678 EVM 上的DDR 存儲器為例,它的組織結構如圖11 所示。請注意,對不同的DDR 存儲器,每一行的大小可能會不同。

圖11 DDR bank 數據組織結構

盡管DDR 存儲器有多個bank,但與SL2 的bank 不同的是,它們并沒有獨立的總線與控制器相連,而是共享相同的總線接口。所以,DDR 存儲器bank 的個數并不直接的影響帶寬,但它卻顯著的影響多個主模塊共享DDR 的效率。

DDR SDRAM 的訪問以行或頁為基礎。一個主模塊在訪問某個頁中的數據之前,這一頁必須首先被“打開”,然后這一頁中的內容才可以被隨意訪問。如果主模塊想訪問同一個bank 中另一頁中的數據,必須先關閉原先的頁,然后打開新的一頁。而頁切換(關閉/打開)操作需要消耗額外的時鐘周期。

每個bank 只可以有一頁被打開,DDR 存儲器的bank 數越多,頁切換的概率就越小。例如,一個主模塊在訪問了bank0 的0 頁后,它可以訪問bank1 的1 頁而不用關閉之前訪問的bank0 的0頁,然后這個主模塊可以自由的在這兩頁之間訪問而不會產生頁切換。包含8 個bank 的DDR 存儲器可以有8 頁同時被打開。

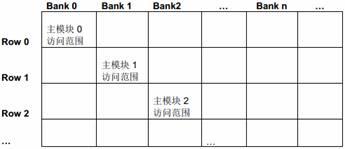

為了測試頁切換的影響,我們定義了兩種測試的數據結構。

圖12 多個主模塊訪問相同DDR bank 的不同頁

上面的情況是最壞的情況,頁切換的額外開銷被最大化。每換一個主模塊訪問就會導致一次頁切換。

下面的情況則是最佳情況,每個主模塊始終訪問打開的頁,而不會有任何頁切換發生。

圖13 多個主模塊訪問不同DDR bank 的不同頁

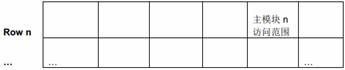

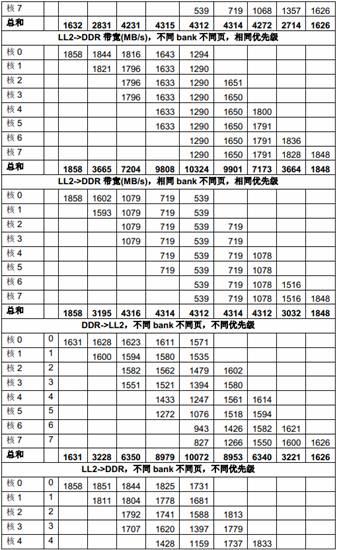

2.2.1 多個DSP 核共享DDR 的性能

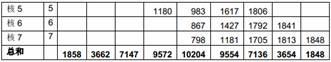

下面的表格列出了不同場景下多個DSP 核共享1GHz C6678 EVM 上64-bit 1333MTS DDR 的性能。每個主模塊反復訪問自己在DDR 中的數據buffer,在相同的時間內(大概2 秒),每個主模塊傳輸的數據量被統計;而每個主模塊獲得的帶寬則由數據量除以時間計算出來。

在這些測試中,DDR 是cacheable 且prefetchable 的,L1D cache 是32KB,L2 cache 是256KB,prefetch buffer 被使能。我們沒有測試Non-cacheable 的情況是因為Non-cacheable 情況下每個核需要的帶寬比cacheable 的情況下要少很多。

在下面的表中,每列是一個測試場景的結果,不同測試場景的主要區別是同時訪問存儲器的主模塊的個數,格子中的數據代表相應的主模塊在這個測試場景下獲得的帶寬,一列中的空格代表對應的主模塊在這個測試場景下未被使用。最后一行中的數據是在這個測試場景下所有主模塊獲得的帶寬的總和。

表10 多個DSP 核共享DDR 的性能

存儲器相關文章:存儲器原理

評論