零基礎學FPGA(四)Verilog語法基基礎基礎(中)

7、結構語句

本文引用地址:http://www.104case.com/article/267552.htm(1)initial語句比較簡單,這里就不多說了。

(2)always語句

always語句在仿真過程中是不斷活動的,always語句后面的語句是否執行,這要看always語句是否滿足觸發條件。因此,always語句只有和時序控制語句結合才能使用,否則就會被死鎖。例如:always areg=~areg;

這個always語句生成一個0延遲的無限跳變過程這時會發生死鎖。但是一旦加上時序控制,這條語句就不一樣了,例如:

always #10 areg=~areg;

這樣的語句就描述的一個周期為20毫秒的跳變信號。所以我們常用這種方法來描述時鐘信號,并作為激勵信號來測試硬件電路。

看下面這個例子

reg [7:0] counter;

reg tick;

always @(posedge areg)

begin

tick=~tick;

counter=counter+1;

end

這個例子就是說每當信號areg上升沿到來時,信號tick取反,計數器counter加一,這種時間控制是always語句最常用的。

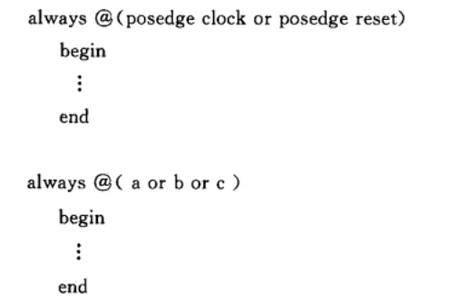

always語句的時間控制模板

如果組合邏輯塊語句的輸入變量過多容易漏掉,例如:

always @(a or b or c or d or e)

這樣的情況下可以用always@ (*)語句來代替,*號自動將所有輸入變量默認為敏感信號。

上面所討論的都是等待信號的值發生變化或者觸發時才執行相應語句,我們也可以用wait語句來用電平敏感來控制。例如

always

wait (count_enable) #20 count=count+1;

意思就是說,當count-enable的值為1時,程序延遲20毫秒后計數。

8、任務與函數

書上寫了關于任務與函數的區別,寫了好多,我覺得區別這兩個概念主要看一點就夠了,就是看有沒有返回值,函數有,任務沒有。舉個例子

switch_bytes (old_bytes,new_bytes);這是個任務,沒有返回值,功能是把新舊兩個字節互換位置。

new_bytes=switch_bytes(old_bytes);這是個函數,功能是把舊字節轉換后賦值給新字節。有返回值。

下面寫一個交通信號燈的程序來學習一下任務這個概念

moudle xiaomo_traffic;

reg clock,red,green,amber;

//定義時鐘,紅燈,黃燈,綠燈

parameter on=1,off=0,red_tics=350.amber_tics=30,green_ics=200;

//定義紅燈等待350個時鐘,黃燈等待30個時鐘,綠燈等待200個時鐘

initial red=0;

initial green=0;

initial amber=0;

//初始化,這里用initial語句保證三條語句同時執行

always

begin

red=on; //紅燈亮

light (red,red_tics); //這里用到任務,功能是等待350個時鐘的時間,聲明看下面程序

amber=on; //黃燈亮

light (amber,amber_tics); //等待30個時鐘

green=on; //綠燈亮

light (green,green_tics); //等待200個時鐘

end

task:light; //命名任務

output color;

input [31:0] tics;

//注意這里的兩個變量要與上面的一一對應,也就是說上面的light(red,red_tics);中的red對應color,red_tics對應tics

begin

repeat(tics); //重復執行tics次下面的語句

@(posedge clock); //等待上升沿,因為這里的tics對應上面的red_tics幾個,所以這里要等待相應個上升沿

color=off; //等到相應個上升沿結束時,相應顏色的燈關閉

end

endtask

//下面就是寫時鐘函數了,用always塊

always

begin

#100 clock=0;

#100 clock=1; //每100毫秒產生一次跳變

end

endmoudle

注意:這個程序要找對一一對應關系,例如脈沖模塊里的clock對應posedge clock中的clock,程序行與行之間是有聯系的,不能隨便聲明

fpga相關文章:fpga是什么

c語言相關文章:c語言教程

評論