零基礎(chǔ)學(xué)FPGA(四)Verilog語法基基礎(chǔ)基礎(chǔ)(中)

4、循環(huán)語句

本文引用地址:http://www.104case.com/article/267552.htmVerilog語法**有4中循環(huán)語句,這里只簡單說一下C語言里沒有的兩種

(1) forever語句

連續(xù)執(zhí)行語句,這種語句主要用在產(chǎn)生周期性的波形,用來做仿真信號。個人理解和always語句差不多的功能,但是,forever語句只能用在initial塊中。

(2)repeat 語句后面接常量表達(dá)式,可以指定循環(huán)次數(shù),例如;

repeat (8)

begin

…

end

表示循環(huán)8次相應(yīng)語句。

5、順序塊和并行塊

所謂順序塊就是前面說的begin…end,他的作用就是把多條語句組合到一起執(zhí)行,在順序塊里面,語句是一條一條順序執(zhí)行的,如果遇到#10延遲語句,延遲也是相對于上一條語句的延遲,這一點(diǎn)比較重要。

相對于順序塊的就是并行塊,用fork…end語句表示,并行塊里的語句是同時執(zhí)行的。

順序塊和并行塊可以嵌套使用。

如果在begin或者fork語句后面加上名字,這個塊語句就成了命名塊,例如

begin :xiaomo

……

end

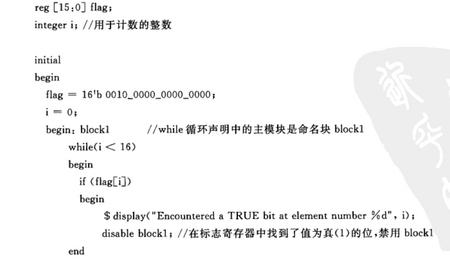

命名塊有什么好處呢?有了命名塊,我們就可以用verilog提供的disable語句來隨時終止命名塊,例如disable xiaomo;這樣,當(dāng)程序運(yùn)行到此時,就會禁用命名塊,就會直接跳出塊語句,相當(dāng)于C語言里面的break語句一樣,看下面這個例子:

6、生成塊

生成塊語句可以動態(tài)的生成Verilog代碼,這一聲明語句方面了參數(shù)化模塊的生成。黨對矢量中的多個位進(jìn)行重復(fù)操作時,或者進(jìn)行多個模塊的實(shí)力引用時,或者在根據(jù)參數(shù)的定義來確定程序中是否應(yīng)該包括末端Verilog代碼的時候,使用生成語句能夠大大簡化程序的編寫過程。

生成語句可以控制變量的聲明、任務(wù)或函數(shù)的調(diào)用,還能對實(shí)力引用進(jìn)行全面的控制。編寫代碼時必須在模塊中說明生成塊的實(shí)例范圍,關(guān)鍵字 generate…endgenerate用來指定該范圍。

Verilog中有三種生成語句的方法,分別是循環(huán)生成,條件生成和case生成。

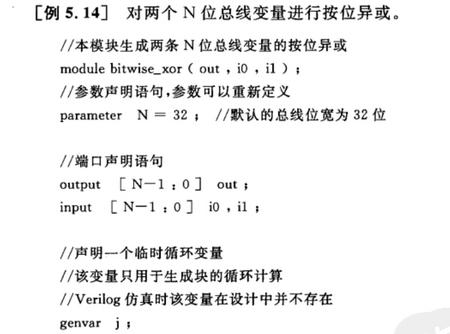

(1)循環(huán)生成

注:genvar 是關(guān)鍵詞,用于生成生成變量,生成變量只存在于生成塊中,在確立后的方針代碼中,生成變量是不存在的。

xor_loop是賦予生成語句的名字,目的在于溝通它對循環(huán)生成語句之中的變量進(jìn)行層次化引用。因此循環(huán)生成語句中的各個異或門的相對層次為:xor_loop[0].gl,xor_loop[1].gl…,xor_loop[31] 這句話什么意思啊

這個例子中的 xor gl (out [ j ] , i0 [ j ], i1 [ j ] );什么意思??求大神指點(diǎn)

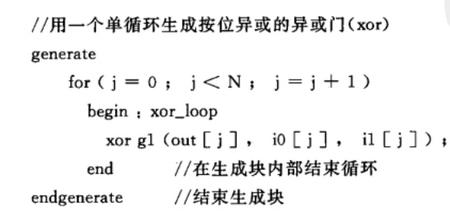

當(dāng)然這個異或門還可用always塊實(shí)現(xiàn)

生成塊程序

generate

for (j=0;j

begin :xiaomo

always @(i0[ j ] or i1[ j ]) out [ j ]=i0[ j ]^i1[ j ];

end

endgenerate

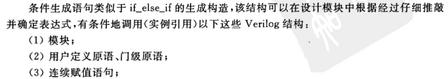

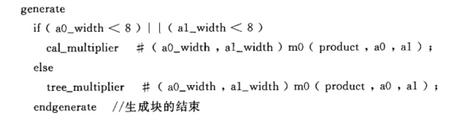

(2)條件生成

下面是一段生成語句

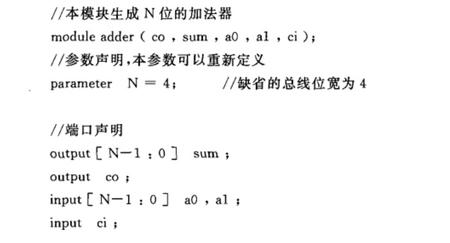

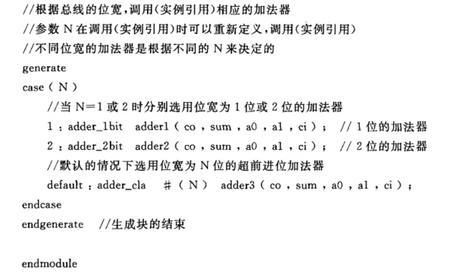

(3)case生成

下面是一個例子使用case語句生成N位的加法器

說實(shí)話上面這些東西我自己也是看的模模糊糊,好多地方不懂,只能先截個圖放這兒了。唉...基礎(chǔ)還是不行啊...

fpga相關(guān)文章:fpga是什么

c語言相關(guān)文章:c語言教程

評論