Giga ADC 介紹及雜散分析(上)

當一個折疊輸出信號不是在線性區域范圍內時,另一個折疊輸出信號恰好在線性區域內,反之亦然。這種方法可以推廣到相位差更小的一組折疊信號的情況,以減小非線性區域的影響。直至,相鄰折疊信號的過零點只相距一個量化單位(LSB)時,每個與折疊電路連接的比較器只需檢出過零點。此時,折疊結構ADC不再要求折疊信號的線性區域范圍,只要求過零點的精度。

在折疊電路設計中,一級折疊電路折疊率不宜過高,這主要是因為,如果一級折疊率過高,那么這么多輸出通過長的走線連接到一起輸出給下一級比較器,寄生電容對于后級的影響變得不可忽略。在TI的Giga ADC中,一般采用多級折疊電路級連的方式,例如,如果要實現一個折疊率為9的電路,采用了兩級折疊級連,每級的折疊率是3,如figure10所示。

2.3.3內插電路

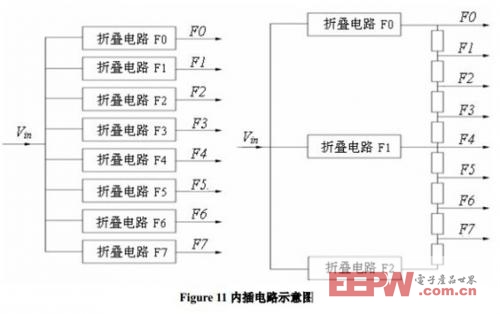

直接利用折疊電路來產生所有2N個過零點,ADC的功耗與輸入電容都很大。通常的解決辦法是采用折疊-內插結構,如Figure11所示。每兩個折疊電路的輸出之間連接一個插值電阻串,利用插值電阻的分壓作用得到兩個折疊電壓信號之間的插值電壓。每個插值節點作為輸出,插值的數目稱為內插率I;Figure11是當I=4的內插結果,兩側為原始的由折疊電路產生的折疊信號,夾在其間的3個信號是被節省的、由內插電路產生的折疊信號。這樣,通過4倍的內插,每4個折疊信號可以節省3個折疊電路。

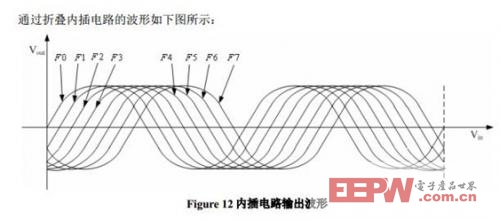

通過折疊內插電路的波形如下圖所示:

2.3.4平均電路

前面提到,影響電路精度的主要誤差是差分信號的偏置誤差。降低差分電路的偏置誤差可以增加晶體管的面積。但由于在折疊電路中,偏置誤差不僅僅來自于差分電路,折疊電路中其它飽和支路的輸出電流也增加了整個電路的偏置誤差,簡單的增加電路晶體管面積并不能有效的降低誤差。由于各個放大電路的偏置誤差是不相關的,這里采用了迭代的技術,使某一輸出節點的偏置誤差不僅僅取決于本身放大電路,還和相鄰其它并行放大電路輸出有關,偏置誤差通過放大電路輸出的迭代而隨機化,降低了整個電路的偏置誤差。

2.4校準電路

前面提到的各種設計電路有效的提高了ADC的線性性能和帶寬,但在TI Giga ADC,仍然集成了校準電路,用以進一步優化ADC的性能。這部分校準電路包括27個高精度校準電壓,采用輪詢的方式依次輸入到輸入級的開關,并根據校準信號的輸出結果通過DAC調整預放大電路的偏置電流,達到校準修正的結果。

通過Figure5可以看到,輸入級的MUX開關,采保電路,輸入buffer的偏置誤差以及折疊電路的偏置誤差等包括在校準環路里,通過校準不僅僅提高了放大電路的線性,而且提高了系統在interleave模式下兩路ADC之間的一致性,改善了系統的雜散性能。

Giga ADC 介紹及雜散分析(下)

評論