一種數字示波器的微處理器硬件電路設計

本設計中,被測信號進入模擬通道調理后送入ADC,ADC對模擬信號采樣、量化后,進入FPGA數據流降速和數據同步處理,然后根據存儲深度要求選擇存入FPGA內部FIFO或者存入片外SRAM,待FPGA內部FIFO或者片外SRAM滿標志有效后,DSP讀取采樣數據存入DDR2 SDRAM,并完成一系列復雜的處理和運算,如FFT、插值和濾波等,再存入在DDR2內拓展的顯示存儲區,待需要顯示時再由DSP讀取顯存中的數據通過內部集成的LCD控制器采用DMA方式將數據送到LCD顯示,完成一次采集過程。

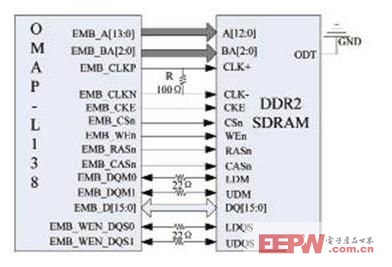

OMAP-L138與DDR2的接口電路設計

OMAP-L138內部集成的DDR2/Mobile DDR控制器可外接工作頻率150MHz的DDR2 SDRAM或者工作頻率133MHz的Mobile DDR。本設計采用DDR2 SDRAM作為系統后級波形數據緩存器。較之SDRAM,DDR2 SDRAM不僅讀寫速度可大幅提高,存儲容量更是得到極大擴展,示波器因而能夠存儲更多波形數據并觀察到更多的波形細節,提高示波器對復雜信號和瞬態信號的捕獲概率。本設計的DDR2 SDRAM選用鎂光公司的DDR2 800內存顆粒,型號為MT47H64M16,容量為1Gbit,核心工作電壓為1.8V,核心工作頻率為400MHz,由于OMAP-L138內部的DDR2控制器最高工作頻率為150MHz,所以此系統中DDR2需要降頻使用。OMAP-L138與DDR2的接口連接示意圖如圖3所示:

圖3 OMAP-L38與DDR2的接口連接示意圖

DDR2的信號線包括時鐘、數據和命令三部分。本設計由DDR2控制器提供差分時鐘CLK+和CLK-給DDR2,,差分時鐘之間并接一個100Ω的匹配電阻,用以消除時鐘的毛刺并限制驅動電流;數據部分主要完成數據傳輸工作,包括數據線DQ[15:0]、數據同步信號DQS(本設計LDQS對應數據線低八位,UDQS對應數據線高八位)、數據信號屏蔽線DM(在突發寫傳輸時屏蔽不存儲的數據,LDM對應數據位低八位DQ[7:0],UDM對應數據線高八位DQ[15:8]),本設計在DQS信號和DM信號上串接一個22Ω的電阻,起抗干擾和濾波作用,提高信號質量;命令部分包括行地址選通信號RASn、列地址選通信號CASn、寫使能信號WEn、片選信號CSn、時鐘使能信號CKE以及芯片內部終端電阻使能ODT,主要完成尋址、組成各種控制命令以及內存初始化工作。本設計由于DDR2控制器內沒有終端電阻,因此將DDR2 SDRAM的ODT信號直接接地使DDR2芯片內的終端電阻無效。

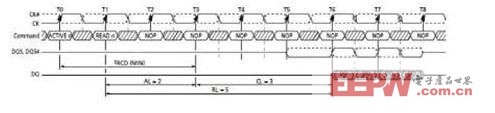

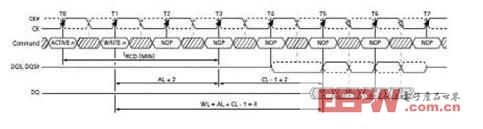

DDR2的讀、寫時序圖分別見圖4和圖5:

圖4 DDR2的讀數據時序圖

圖5 DDR2的寫數據時序圖

評論