一種數字示波器的微處理器硬件電路設計

引言

隨著通信技術的迅猛發展,電信號越來越復雜化和瞬態化,開發人員對測量領域必不可少的工具——數字示波器的性能提出了越來越高的要求。最大限度提高實時采樣率和波形捕獲能力成為了國內外眾多數字示波器生產廠商研究的重點,實時采樣率和波形捕獲率的提高又必然帶來大量高速波形數據的傳輸、保存和處理的問題。因此,作為數字示波器數據處理和系統控制的中樞,微處理器性能至關重要。本文選用TI公司的雙核DSP OMAP-L138作為本設計的微處理器,并實現了一種數字示波器微處理器硬件設計。

數字示波器的基本架構

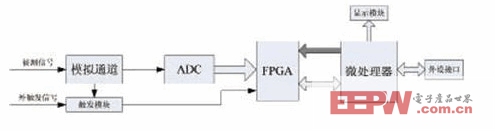

目前數字示波器多采用DSP、內嵌微處理器型FPGA或微處理器+FPGA架構。雖然內嵌微處理器型FPGA靈活性強,可以充分進行設計開發和驗證,便于系統升級且FPGA外圍電路簡單。但是該類型FPGA屬于高端FPGA,價高且供貨渠道難得,不適合低成本的數字示波器使用。若單獨使用DSP,雖然其數據處理能力強大,運行速度較高,但DSP的控制能力不突出,且數字示波器的采樣率越來越高,DSP內部不能做數據流降速和緩存,當設計采用高實時采樣率的ADC,就得選用頻率更高且內部存儲資源更豐富的DSP,而此類DSP一般都價格昂貴,同樣不適合低成本的數字示波器使用。因此,微處理器+FPGA架構的方案是本設計首選。微處理器+FPGA架構的數字示波器的系統結構圖如圖1所示:

圖1 微處理器+FPGA架構的數字示波器系統結構圖

被測信號經模擬通道運放調理后送到ADC器件;ADC轉換器將輸入端的信號轉換成相應的數字信號并經過FPGA緩存和預處理;微處理器對采樣得到的數字信號進行相關處理與運算;最后將波形送到屏幕上顯示,完成一次采集過程。同時采集過程中觸發電路不斷監測輸入信號,看是否出現觸發狀態,觸發條件決定了波形的起始位置,觸發系統能夠保證被測波形能夠穩定的顯示到屏幕上。

評論