FPGA最小系統之:實例2 在Xilinx的FPGA開發板上運行第一個FPGA程序

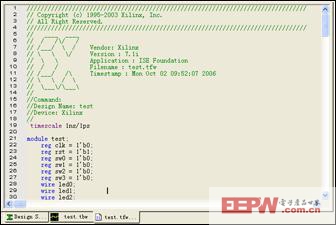

然后在進度瀏覽器的“Process View”對話框里面雙擊“View Generated Test Bench As HDL”圖標,就能看見ISE根據剛才設置的波形文件自動生成的測試文件,如圖2.93所示。

圖2.93 生成的測試代碼

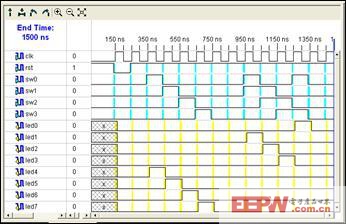

在進度瀏覽器中雙擊【Generate Expected Simulation Result】,彈出兩個對話框,都選擇是(Y),將看見生成的預期輸出波形,如圖2.94所示。

圖2.94 預期仿真波形

在進度瀏覽器中雙擊“Add Test Bench to Project”,將測試波形添加到工程里面。將會看到工程瀏覽器中test文件的圖標由 變成

變成 。

。

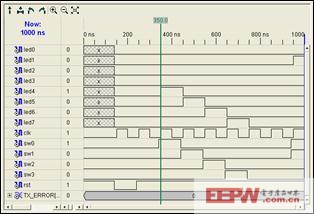

如圖2.95所示,在進度瀏覽器中雙擊“Simulate Behavioral Model”將對工程進行行為仿真,仿真結果如圖2.96所示。

圖2.95 運行功能仿真

圖2.96 功能仿真結果

從圖中可以看出功能仿真結果符合設計要求,可以繼續進行下面的設計。如果此處仿真發現設計功能不符合要求,則要對原代碼進行修改,直到仿真結果符合設計要求為止。

4.約束設計

在源程序輸入完成以后,就可以設置約束,規劃布局布線了。

約束有很多種:時序約束(Timing Constrains)、管腳約束(Assign Package Pins)以及面積約束(Area Const- raints)等。

如圖2.97所示是ISE進度瀏覽器中包含的用戶約束的選項。

圖2.97 設置約束

(1)時序約束。

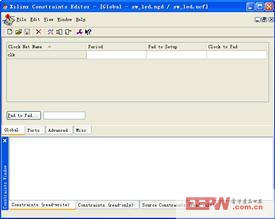

時需約束主要約束設計的時序和時鐘頻率,雙擊圖2.97中的“Create Timing Constraints”圖標,ISE將打開約束編輯器,如圖2.98所示。

圖2.98 時序約束界面

在約束編輯器里面有4個復選頁,定義如表2.5所示。

表2.5 屬性定義

屬 性 | 定 義 |

Global | 用于附加全局約束,包括周期約束,輸入延遲約束和輸出延遲約束 |

Ports | 附加端口約束,可以對每一個端口進行單獨設置,包括物理位置、輸入延遲和輸出延遲。同時,也可以設置分組,進行分組約束 |

Advanced | 附加分組約束(TNM/TNM_NET/TIMEGRP)和時序約束(FROM_TO/TIG O/OFFSET)等 |

Misc | 附加專用約束,包括電壓、初始值等 |

| 注意 | 附加約束的原則是先加全局約束后加分組約束。 |

在本實例中只做簡單的時鐘約束。在clk的period中輸入:20ns HIGH 50%,即設置時鐘的周期和占空比。設置后保存,完成時序約束。

(2)管腳約束。

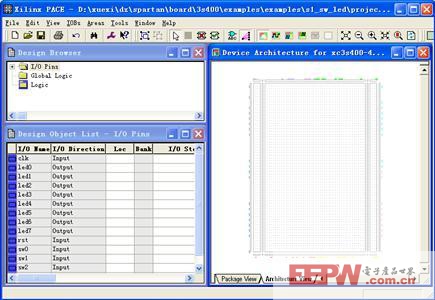

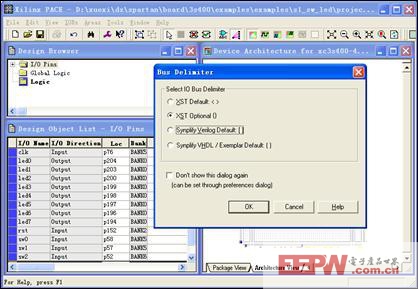

管腳約束即約束工程設計源文件與選定器件對應的輸入/輸出管腳屬性。雙擊圖2.97中的“Assign Package Pins”圖標,ISE將打開PACE工具,如圖2.99所示。

通過圖2.99的“Design Object List”對話框里面的Loc列,可以為設計添加輸入/輸出管腳,添加形式為“Pxxx”或者“pxxx”。其中P/p代表Pin,xxx是數值。

(3)面積約束。

面積約束目的在于規劃FPGA里面的邏輯使用大小。雙擊圖2.97中的“Create Area Constraints”圖標,ISE同樣打開PACE工具,面積約束和管腳約束用的是一個界面。在面積約束里面我們可以對設計使用的資源面積加以規劃,控制使用資源在FPGA里面的位置。

這里只使用到管腳約束,按照按鍵和LED燈與FPGA的連接,輸入管腳分配,然后保存分配。在保存選項中,選擇“XST Optional”,如圖2.100所示,關閉對話框,完成約束設計。

圖2.99 管腳約束工具PACE

圖2.100 保存管腳約束結果

評論