FPGA最小系統(tǒng)之:實(shí)例2 在Xilinx的FPGA開發(fā)板上運(yùn)行第一個FPGA程序

3.綜合及仿真

(1)綜合。

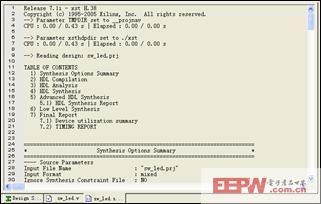

在“Process View”對話框里面雙擊“Synthesize – XST”,開始進(jìn)行工程的綜合,如圖2.81所示。

綜合主要檢查源文件程序里面的語法錯誤(Check Syntax),雙擊“View Synthesis Report”可以觀察綜合的結(jié)果報(bào)告,如圖2.82所示。

圖2.82 綜合報(bào)告

如果在這步發(fā)現(xiàn)源程序的設(shè)計(jì)語言有語法毛病,就會彈出Error警告。這樣就可以根據(jù)報(bào)錯的位置,在源程序里面查找錯誤位置,修改好以后重新進(jìn)行綜合,直至無錯誤為止。

(2)綜合后仿真。

這里的仿真是綜合后的仿真,也可以稱為功能仿真。仿真時(shí)并不考慮工程的約束條件及器件的資源使用狀況,因此不會產(chǎn)生仿真延遲。這里使用的是ISE自帶的仿真工具進(jìn)行綜合后仿真。下面是仿真的步驟。

① 產(chǎn)生仿真文件。

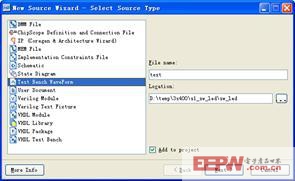

如圖2.76的方式,在“New Source”對話框里面選擇創(chuàng)建Test Bench Wavefrom文件,如圖2.83所示。

單擊“Next”按鈕,在如圖2.84所示對話框中為Test Bench指定源文件。如圖所示在源文件對話框中只有一個文件,這是因?yàn)槲覀冎粸楣こ烫砑恿艘粋€設(shè)計(jì)文件。如果我們?yōu)楣こ烫砑恿藥讉€設(shè)計(jì)文件,在這個對話框中,將出現(xiàn)多個源文件。此時(shí)用戶可以選擇需要進(jìn)行仿真的源文件即可。

圖2.83 新建Test Bench對話框

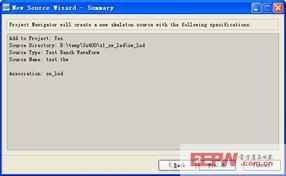

在本訓(xùn)練中,將要進(jìn)行仿真的源文件是sw_led,如圖2.84所示。單擊“Next”按鈕完成仿真文件的產(chǎn)生,如圖2.85所示。

圖2.84 為Test Bench指定源文件

圖2.85 Test Bench信息對話框

單擊“完成”按鈕,ISE將創(chuàng)建名為test.tbw的仿真文件,同時(shí)彈出如圖2.86所示的對話框。在該對話框中,用戶可以對仿真的時(shí)間參數(shù)進(jìn)行設(shè)置。

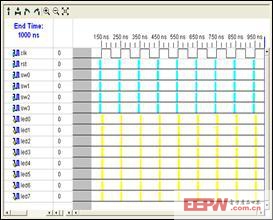

在這個對話框中,包括時(shí)鐘信息、時(shí)鐘時(shí)間信息、全局信號、仿真時(shí)間等多個參數(shù)都可以進(jìn)行設(shè)置。按照仿真需求修改好時(shí)間參數(shù)以后,單擊“OK”按鈕就能在ISE的工作區(qū)里面看見新建的波形文件了,如圖2.87所示。

在波形文件里面,clk是時(shí)鐘信號,在前面的時(shí)間參數(shù)設(shè)計(jì)里面已經(jīng)設(shè)置好了。用戶若需要對時(shí)鐘進(jìn)行更改,可選擇執(zhí)行“Test Bench”→“Rescale Timing…”命令,彈出修改時(shí)間參數(shù)的對話框,如圖2.88所示。

圖2.86 仿真時(shí)間參數(shù)設(shè)置對話框

圖2.87 時(shí)鐘波形 圖2.88 修改時(shí)間參數(shù)對話框

同樣也可以執(zhí)行“Test Bench”→“Set End of Test Bench…”,在彈出的對話框里面修改仿真波形的截止時(shí)間,如圖2.89所示。

圖2.89 截止時(shí)間設(shè)置對話框

單擊“OK”按鈕就會發(fā)現(xiàn)仿真波形的時(shí)間長度由1000ns變成了2000ns。

② 添加仿真激勵。

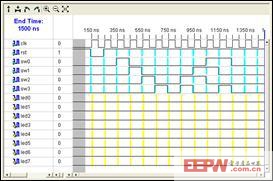

要進(jìn)行仿真,還需要為仿真添加激勵。這里可以通過點(diǎn)擊波形圖中的藍(lán)色方塊來設(shè)置輸入波形電平的高低,如圖2.90所示。

圖2.90 設(shè)置輸入電平

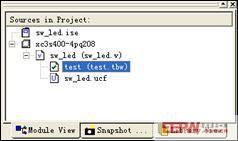

設(shè)置好以后一定不要忘記保存波形文件。保存以后就會在工程瀏覽器的當(dāng)前工程的子目錄下看見剛生成測試的文件,如圖2.91所示。

圖2.91 保存仿真文件到工程

③ 仿真。

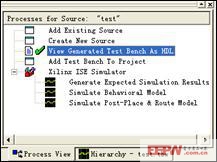

首先在工程瀏覽器的【Module View】里面選擇“test(test.tbw)”。

圖2.92 由波形文件生成測試代碼

評論