ARM存儲器之:存儲管理單元MMU

⑤域控制位失效

域控制位失效包括兩種類型。一種基于段的存儲訪問域控制失效。在一級描述符中包含4位的域標識符。該標識符指定了本段所屬的域,在MMU讀取一級描述符時,它檢查域訪問控制寄存器c3中對應于該域的控制位,如果相應的兩位控制位為0b00,說明該域不允許存儲訪問,這時,就產生了基于段的存儲訪問域控制失效。第二種是基于頁的存儲訪問中域控制位失效。在一級描述符中包含4位的域標識符。該標識符指定了本頁所屬的域,在MMU讀取一級描述符時,它檢查域訪問控制寄存器c3中對應于該域的控制位,如果相應的兩位控制位為0b00,說明該域不允許存儲訪問,這時就產生了基于頁的存儲訪問域控制失效。

⑥訪問權限失效

訪問權限失效的檢查是在域控制位失效檢查時進行的。這時如果域訪問控制器中對應于該域的控制位為0b01,則要進行相應的權限檢查。訪問權限失效有兩種類型。一種基于段的存儲訪問權限控制失效,對于基于段的存儲訪問,在一級描述符中包含一個兩位的訪問權限控制位AP。如果字段AP標識了不允許進行相關存儲訪問時,產出基于段的存儲訪問權限控制失效。第二種是基于頁的存儲訪問控制失效。對于基于頁的存儲訪問,在二級描述符中定義的可能為大頁、小頁或者微頁。當二級描述符中定義的為微頁時,該二級描述符中包含一個對應于該微頁的訪問控制字段AP,如果字段AP標識了不允許進行相關的存儲訪問,這時產生基于子頁的存儲訪問權限控制失效。同樣,當二級頁表描述符中定義的為小頁或大頁時,操作過程同微頁。

(3)外部存儲訪問失效

除處理器內部MMU向CPU報告錯誤外,ARM體系結構還定義了一個外部訪問中斷引腳。該引腳可以用于外部存儲器向CPU訪問失效異常。但是,并不是所有失效異常都可以通過這種方式報告,所以該引腳在連線時要非常注意。下面列舉了存儲訪問操作,可以通過這種機制中止和重啟動。

·讀操作(reads)。

·非緩存的寫操作(unbufferedwrites)。

·一級描述符預取(first-leveldescriptorfetch)。

·二級描述符預取(second-leveldescriptorfetch)。

·非緩存的信號量操作(semaphoresinuncachable/unbufferablememoryareas)。

在Cache預取時,可以在任意字時終止存儲訪問過程。如果存儲訪問發生在存儲器想要獲取的數據中,這時該存儲訪問將立即被中止。如果產生中止的數據是在Cache預取時,從存儲器順序讀出的,那么直到這些數據被存儲器訪問時,該存儲訪問才會被中止。

帶緩存的寫操作不能通過這種方式向CPU報告異常。因此,在系統中標記為可外部中止的存儲區域不要進行可緩存的寫操作。

15.5.9快速上下文切換擴展(FCSE,FastContextSwitchExtension)

(1)快速上下文切換擴展原理

快速上下文切換擴展(FCSE,FastContextSwitchExtension)是MMU中的一個附加硬件,用于提高ARM嵌入式系統的系統性能。FCSE使得多個獨立任務可以運行在一個固定的重疊存儲空間中,而在上下文切換時,不需要清理(clean)或清除(flush)Cache和TLB。FCSE主要特征就是不需要清除Cache和TLB。

通常情況下,如果兩個進程占有的虛擬地址空間有重疊,系統在兩個進程之間進行切換時,必須進行虛擬地址到物理地址的重映射。而虛擬地址到物理地址重映射涉及到重建MMU中頁表,而且Cache及TLB中的內容都必須使無效。這樣操作將帶來巨大的系統開銷,一方面重建MMU和使無效Cache及TLB的內容需要很大的開銷,另一方面重建Cache和TLB內容也需要很大的開銷。

快速上下文切換擴展的引入避免了這種開銷。它位于CPU和MMU之間,如果兩個進程使用了同樣的虛擬地址空間,則對CPU而言,兩個進程的空間地址是一樣的。快速上下文切換擴展對各進程的虛擬地址進行變換,這樣系統中CPU之外的部分看到的是經過快速上下文切換擴展變換的虛擬地址。快速上下文切換擴展將各進程的虛擬空間變換成不同的虛擬空間。這樣在進行進程間切換時就不需要進行虛擬地址到物理地址的重映射。

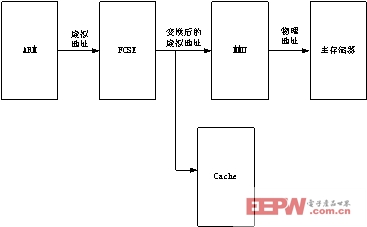

快速上下文切換擴展將CPU發出的每個虛擬地址按照上述的規則進行變換,然后發送到系統中的其他部分。變換過程如圖15.37所示。

圖15.37快速上下文切換擴展變換過程

使用快速上下文切換擴展,虛擬存儲管理增加了一次地址轉換。快速上下文切換擴展在虛擬地址到達Cache和TLB前,使用一個特殊的、包含進程ID值的重定位寄存器來修改虛地址。把第一次變換前的地址稱為虛地址VA(VirtualAddress),把第一次變換后的地址稱為修改后虛擬地址MVA(ModifiedvirtualAddress)。

這樣,任務間的切換就不用涉及到改變頁表,只需簡單地將新任務的進程ID寫到位于CP15地FCSE進程ID寄存器。正是因為任務切換不需要改變頁表,因而切換后Cache和TLB中的值依然保持有效,不需要清除。

ARM系統中,4GB的虛擬空間被分為128個進程空間快,每個進程空間塊大小為32MB。每個進程空間塊中可以包含一個進程,該進程可以使用虛擬地址空間0x00000000~0x01ffffff,這個地址范圍也就是CPU看到的進程的虛擬空間。系統128個進程空間塊的編號為0~127,編號為1的進程空間塊中的進程實際使用虛擬地址空間為1×0x02000000~1×0x02000000+0x01ffffff。這個地址空間是系統中除CPU之外的其他部分看到的該進程所占有的虛擬地址空間。

由地址VA到MVA的變換算法如下所示。

MVA=VA+(ox02000000×進程ID)

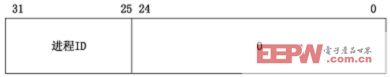

保存在CP15寄存器c13寄存器中的值包含進程ID,c13中從bit[31]~bit[25]共7位標識進程ID,因此可以有128個進程。寄存器格式如圖15.38。

圖15.38快速上下文切換寄存器c13

訪問寄存器c13的指令格式如下所示:

MCRp15,0,Rd>,c13>,c0,0

MRCp15,0,Rd>,c13>,c0,0

其中,在讀操作時,結果中位[31:25]返回PID,其他位的數值是不可預知的。寫操作將設置PID的值。

當PID=0時,MVA=VA,相當于禁止了FCSE。系統復位后PID為0。

當正在運行的進程訪問別的進程時,被訪問的進程標識不能為0。這時,CPU發生的地址VA的高7位不是全0。

完整的VA到MVA的變換算法如下所示。

If(VA[31:25]==0b0000000)then

MVA=VA|(PID<<25=

Else

MVA=VA

存儲器相關文章:存儲器原理

評論