ARM體系結構的發展之:ARMv6增加的系統支持

16.2ARMv6增加的系統支持

為了滿足目前無線網絡、汽車電子和消費類電子產品不斷增長的市場需要,ARM公司在ARMv6中引入新的技術和結構組成,包括增強的DSP支持和對多處理器環境的支持。

本文引用地址:http://www.104case.com/article/257007.htm16.2.1存儲管理

由于在ARMv6體系結構中引入新的存儲管理機制,處理器的整體性能得到提高。在新的體系結構中,平均指令預取和數據等待時間大幅度減少,存取過程中Cache命中率顯著提高。由于存儲機制的改善,系統整體性能的提高達到30%。

另外,存儲系統的改善使系統總線(BUS)使用更加合理,從而減少了系統總線使用頻度,降低了系統功耗。

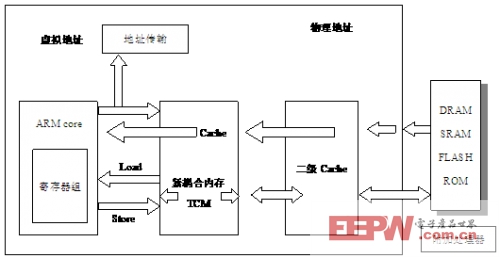

圖16.2顯示了ARMv6體系結構存儲系統示意圖。

圖16.2ARMv6存儲系統示意圖

1.ARMv6L1Cache

ARMv6采用“分層”的存儲管理,存儲層次的最頂層在處理器內核中。該存儲器被稱為寄存器文件(registerfile)。這些寄存器被集成在處理器內核中,在系統中提供最快的存儲訪問。

ARMv6體系結構處理器使用物理索引Cache(Physicallytaggedcaches),即地址轉換在CPU和Cache之間,這樣就減少了CPU在運行大的操作系統時由于上下文切換而帶來的系統開銷。使用這種物理Cache,可以使CPU的整體性能提高近20%。

為了減少在內容轉換時,刷新Cache的CPU開銷,ARMv6將L1Cache構建為使用物理尋址的存儲系統。系統中設有TCM作為物理可尋址的快速訪問內存,存在于存儲系統中,作為Cache的補充。無論Cache還是TCM,都可以配置為指令和數據分離的Harvard架構或指令和數據統一的馮·諾依曼架構。另外,L1DMA子系統可以使數據在沒有CPU參與的情況下,直接和TCM進行數據傳輸。

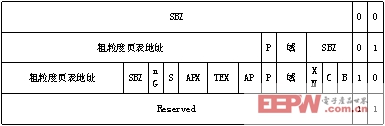

2.頁表格式

在ARMv6體系結構中,頁表格式也發生了變化。圖16.3顯示了新的一級頁表格式。

圖16.3ARMv6頁表格式

協處理器CP15中的XP-bit可以指定是否使用這種新的頁表格式。如果不設置該位,則系統繼續使用ARMv5架構的頁表格式。

從圖16.3可以看出,新的頁表格式增加了以下特性:

·XN:從不執行位(executeneverbit)。

·nG:非全局地址映射位(notGlobalbitforaddressmatching)。

應用程序空間指示ASID(ApplicationSpaceIdentifier)是ARMv6體系中增加的又一關鍵特性。當nG位置位時,地址轉換使用虛擬地址和ASID相結合的方法以減少上下文切換的時間。同時,應用程序空間指示提供了一種任務可知調試方法(task-awaredebugging)。

有關ARMv6存儲系統的詳細內容請參閱ARM相關文檔。

3.增加的頁表基地址寄存器

為了提高地址轉換的處理速度,ARMv6體系結構中增加了一個新的頁表基地址寄存器,以存儲二級頁表的基地址。CP15同時支持TTBR0和TTBR1。專門的控制寄存器用來保存用戶設定的整數N,N的取值范圍為0~7。當N的值不等于0時,0~232-N的地址空間使用TTBR0,而其他空間使用TTBR1進行傳輸控制。一級頁表根據N取值的不同,占有128bytes~16KB存儲空間。

16.2.2多處理單元支持

由于片上系統Soc結構的復雜化,ARM內核現在經常被用于有多個處理單元的設備,這些處理單元競爭使用系統的共享資源。為了滿足多處理單元任務間同步的需要,Load/Store互斥指令引入到新的ARMv6體系結構中來。新指令包括:

·LDREX:加載互斥指令。

·STREX:存儲互斥指令。

LDREX指令從存儲器中裝載一個值到寄存器,在處理這個數據時,不會有任何其他因素改變該值。STREX指令存儲一個值到寄存器,并返回一個指示值。

16.2.3異常處理和中斷

ARMv6體系結構提供了對向量中斷(vectoredInterrupt)的支持。向量中斷控制器(VIC,VectoredInterruptController)由CP15的寄存器1中的VE–bit來控制。當向量中斷控制器使能時,該控制器可以向CPU提供發生中斷的向量。

另外,在ARMv6的體系結構中,程序狀態寄存器CPSR擴展了A位來控制Abort異常。這種機制類似于程序狀態寄存器CPSR中I和Fbit對IRQ和FIQ的控制。

操作系統通常在堆棧中保存一次中斷或異常處理的返回狀態。ARMv6增加了新的指令來提高這類操作的效率。這種操作在中斷/調度程序驅動系統中,出現的頻率是很高的。這些新增加的指令包括:

·SRS:保存返回狀態在特定模式的堆棧中。

·RFE:異常返回。

·CPSID/CPSIE:改變處理器狀態,開中斷或關中斷。

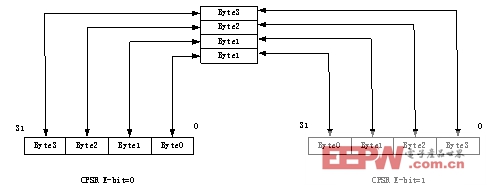

16.2.4混和大小端支持

AMRv6體系結構中增加了同時處理大端和小端數據的能力。新增加了指令SETEND來設置一段代碼處理數據的字節排列方式,另外還增加了一些單獨的處理指令來提高在混和大小端環境下的處理效率。

指令SETEND的標準格式如下:

SETENDendian_specifier>

該指令根據參數endian_specifier>的值來改變默認的數據端格式。

SETEND指令的設置直接和程序狀態寄存器CPSR中新增加的E位相對應。E位對數據大小端的控制如圖16.4所示。

16.2.5對媒體處理的支持

為了進一步提高體系結構的DSP和媒體處理能力,單指令流多數據流(SIMD)技術被引入到ARMv6體系結構中。這種技術對于處理大量復雜運算和并行地存儲大流量數據十分有效。

圖16.4E位對數據大小端的控制

ARMv6對SIMD的實現簡單而又不失其靈活性。它將現存的32位ARM數據通道劃分成4個8位或2個16位的片段,為SIMD操作增加了獨立的數據總線。這種實現方法硬件代價小,遵循了ARM低功耗、高計算效率的設計原則。

為了支持SIMD算法,ARMv6中引入一些新的指令,有關這些指令的詳細信息請參閱ARM的相關文檔。

評論