ARM存儲器之:存儲管理單元MMU

下面的例子顯示了一個使TLB無效的過程。

【例】一個使TLB無效的過程。

MOVr1,0;

MCRp15,0,r1,c8,c7,0

(2)鎖定TLB

由于對TLB表的查詢經常會使系統訪問內存(要查詢的段、頁不在TLB中),這就使得系統的平均訪問時間大大增加。對于實時系統,就需要將一些關鍵的頁表項鎖定在訪問速度相對較快的TLB中。

ARM920T、ARM922T、ARM926EJ-S、ARM1022E和ARM1026EJ-S內核版本支持TLB轉換數據的鎖定。如果TLB中的某一行是鎖定的,則當TLB清除命令發出時,它仍然保留在TLB中。

與TLB鎖定相關的操作可以通過對CP15寄存器r10編程來實現。

各種ARM核的可用鎖定命令如表15.31所示。

表15.31 訪問TLB鎖定寄存器的命令

命令 | MCR指令 | Rd的值 | 支持的內核 |

讀數據TLB鎖定寄存器 | MRCp15,0,Rd,c10,c0,0 | TLB鎖定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

寫數據TLB鎖定寄存器 | MCRp15,0,Rd,c10,c7,1 | TLB鎖定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

讀指令TLB鎖定寄存器 | MRCp15,0,Rd,c8,c5,0 | TLB鎖定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

寫指令TLB鎖定寄存器 | MCRp15,0,Rd,c8,c5,1 | TLB鎖定 | ARM920T、ARM922T、ARM926EJ-S、ARM1022E、ARM1026EJ-S、StrongARM、Xscale |

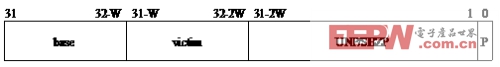

其中Rd的格式如圖15.35所示。

圖15.35Rd格式詳解

其中,

·W=log2N,N為TLB中入口(entry)的個數。對ARM920T、ARM922T、ARM926EJ-S、ARM1022E版本的內核來講,W=6;而對于ARM1026EJ-S內核版本,W=3。

·victm位域:確定下次被換出的TLB入口(entry)。

·base位域:從第0個入口(entry)到base−1入口的TLB值,被鎖定。

鎖定TLB中N條地址入口的操作序列如下。

①確保在整個鎖定過程中不會發生異常中斷,可以通過禁止中斷等方法實現。

②如果鎖定的是指令TLB或指令/數據統一的TLB,將base=N、victim=N、P=0寫入寄存器c10。

③使整個將要鎖定的TLB無效。

④如果要鎖定指令TLB,確保與鎖定過程有關的指令地址變換地址入口已經加載到指令TLB中。

| 注意 | 在此過程中,TLB的一個地址變換入口可以涵蓋所有與鎖定TLB相關的指令。這通常是由使整個TLB無效后的第一條指令實現的。 |

如果要鎖定的是數據TLB,確保與鎖定過程有關的數據地址變換地址入口已經加載到數據TLB中。

| 注意 | 在此過程中避免使用內嵌語法(inlineliteral)。所有鎖定TLB用到的數據可以被TLB中一個地址變換條目所覆蓋。 |

如果系統使用統一的數據TLB和指令TLB,上述兩條都要保證。

⑤對于I=0到N,重復執行下列操作:

·將base=I、victim=I、P=1寫入寄存器c10中;

·將每一條想要鎖定到TLB的變換地址入口讀取到TLB中。對于數據TLB和數據/指令統一的TLB可以使用LDR指令讀取一個涉及該變換地址入口的數據,將該地址變換入口讀取到TLB中。對于指令TLB,通過操作寄存器c7,將相應的變換地址讀取到指令TLB中。

⑥將base=N、victim=N、P=0寫入寄存器c10中。

要解除TLB中被鎖定的變換地址入口,可以使用下面的操作序列。

①通過操作寄存器c8,使TLB中各被鎖定的變換地址入口無效。

②將base=0、victim=0、P=0寫入寄存器c10中。

15.5.8存儲訪問失效

ARM中有兩種存儲訪問失效(Fault)可以導致處理器停止執行。

·MMU失效(MMUFault):由MMU檢測到失效(Fault)并通知處理器。

·外部存儲器訪問中止(ExternalAbort):由外部存儲器向存儲器報告無效的存儲器訪問請求。

上述兩種情況統稱為存儲訪問中止(Abort)。如果存儲訪問中止發生在數據訪問周期,CPU將產生數據訪問中止異常中斷(DataAbort);如果存儲訪問發生在指令預取周期,當該指令執行時,CPU產生指令預取異常中斷(PrefetchAbort)。

| 注意 | 預取指令時發生錯誤,只有當該指令執行時,CPU才會產生指令預取異常中斷。 |

(1)MMU失效

MMU可以產生4種類型的訪問失效,分別是:

·地址對齊失效(AlignmentFault);

·地址變換失效(TranslationFault);

·域控制失效(DomainFault);

·訪問權限控制失效(PermissionFault)。

存儲系統可以中止3種類型的存儲訪問:

·Cache行預取(linefetch);

·無Cache和寫緩存的存儲器訪問(uncachedorunbufferedaccesses);

·傳輸表訪問(translationtableaccesses)。

MMU失效優先于外部存儲器訪問中止請求。當存儲訪問失效發生時,系統控制協處理器中有兩個寄存器分別負責保存發生中止的失效狀態和地址。

| 注意 | 如果一條指令在預取階段發生錯誤,它仍將進入指令流水線,直到該條指令被執行時,預取異常才發生。但當預取錯誤指令在進入執行階段前,指令發生跳轉,那么該預取異常不會發生,協處理器錯誤寄存器的狀態也不會被更新。 |

(2)MMU中與存儲訪問失效相關的寄存器

MMU中與存儲訪問失效相關的寄存器有兩個:

·失效狀態寄存器(FSR,FaultStatusRegister);

·失效地址寄存器(FAR,FaultAddressRegister)。

失效狀態寄存器是協處理器寄存器c5。失效地址寄存器為協處理器寄存器c6。

當存儲訪問失效發生時,失效狀態寄存器中的字段被更新以反映所發生的存儲訪問失效的相關的信息,包括存儲訪問所屬的域以及存儲訪問的類型。同時存儲訪問失效的虛擬地址被保存到地址寄存器c6中。

在數據訪問周期發生存儲訪問失效更新了失效狀態寄存器后,如果系統尚未進入存儲異常模式,這時發生了指令預取引起的存儲失效,則該指令預取引起的訪問失效將不會更新失效狀態寄存器的值。這樣就保證了數據訪問周期發生的存儲訪問失效狀態信息不會被指令預取周期發生的存儲訪問失效破壞。

存儲器相關文章:存儲器原理

評論