一種于FPGA的高速導航解算系統設計與實現

圖2為導航解算FPGA功能仿真時序圖,以此估算模塊計算所消耗的時間。一次姿態解算需要230個時鐘周期,一次導航解算需要980個時鐘周期,那么在50 MHz的系統時鐘下,姿態解算需時4.7微秒,導航解算需時20微秒。導航解算系統功能仿真結果與計算機計算結果進行對比,仿真步長為0.1秒,仿真輸入參數如表2所示,計算結果如表3所示,通過比對可以發現,FPGA的計算結果與MATLAB計算結果沒有偏差,說明導航解算系統能夠正確地進行導航信息的解算。

本文引用地址:http://www.104case.com/article/256592.htm

3 實驗結果與誤差分析

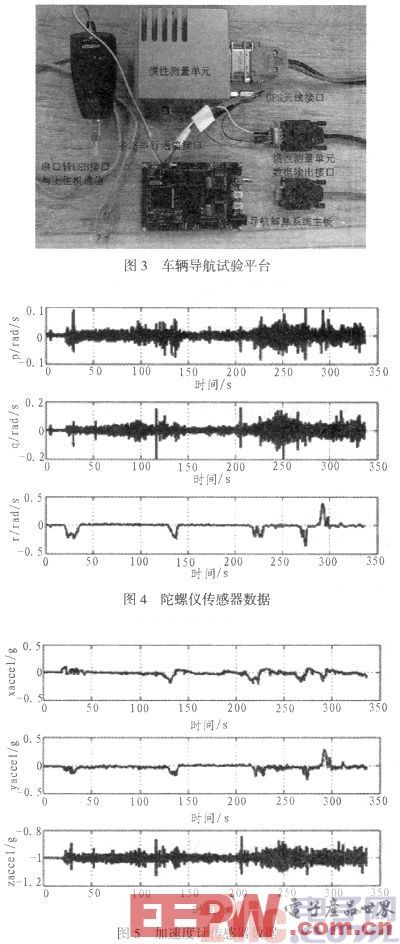

在一輛普通轎車上進行導航實驗,系統的搭建如圖1和圖3所示。系統的核心是一塊承擔數據處理任務的FPGA,在芯片外接合適的IMU,IMU的功耗和體積基本決定了導航系統的功耗和體積。所以整個導航系統的結構是簡單和小巧的而且節能的。

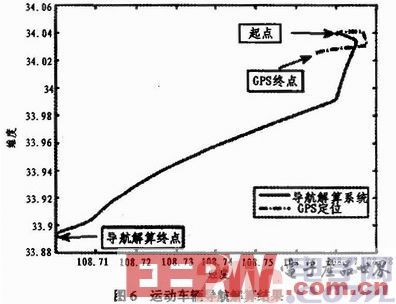

實驗進行了340秒,如圖4和圖5所示,依次是三軸陀螺儀傳感器數據和三軸加速度計傳感器數據。位置曲線如圖6所示,實線是導航解算系統解算的位置信息,虛線是GPS獲得的實際位置信息。可以發現導航解算系統良好地跟蹤了實際位置變化趨勢,但是隨著時間的推移,導航解算系統解算出的位置信息與實際位置信息偏差越來越大。

導航解算系統的誤差引入主要因為基于MEMS的慣性傳感器的誤差較大,使用單一傳感器進行姿態和位置解算會在姿態計算和速度計算環節兩次引入積累誤差。在實際使用中,載體使用的戰術級高精度IMU,在一定的使用時間內,導航系統不會產生很大的積累誤差。除此之外,發揮本系統動態特性好、更新速率快的優勢,借助最優估計的方法,通過進行多種傳感器的信息融合也可以收斂誤差。

4 結論

針對現有小型無人機導航解算系統解算速度慢、多處理器臃腫可靠性差的缺點,文中提出了一種并行化的導航解算方法,并搭建了一種僅使用單一FPGA芯片為數據處理核心的小型高速導航解算系統,功能仿真驗證了導航解算的高速性和準確性。車載實驗驗證了系統可以在實際中完成導航信息的解算工作。根據一次結算消耗時間可知系統理論擁有50 000 Hz的導航解算能力,在實際使用中,輔以足夠精度的高速IMU,系統將會發揮小型化、高速率和低功耗的優勢,在相關的小型無人機導航系統設計領域有重要借鑒意義。

fpga相關文章:fpga是什么

可控硅相關文章:可控硅工作原理

比較器相關文章:比較器工作原理

評論