測試3G手機的DigRF

DigRF準備替換RF與基帶半導體器件之間的兩種主要形式的數據通信路徑:模擬信令,以及針對具體設計的私有數字信令(并行或串行)。MIPI(移動業處理器接口)聯盟正在致力于采用DigRF(數字射頻)標準,用一種基于分組的公共數字串行接口代替各種類型的I/Q(同相位/正交相位)信令接口。一個MIPI聯盟工作小組已開發了用于2.5G和3G手機標準的DigRF規范,預計其后版本會增加支持4G標準的數據流量。

使用DigRF這種標準接口可以使設計者在元件選擇時有更多的靈活性。例如,一名設計者可能準備從某家供應商采購一種高價的基帶IC(可能是手機中最貴的芯片之一),而從其它供應商處購買RF、電源管理和其它器件。然而,DigRF技術在促成通用產品的極端靈活性時也帶來了挑戰,會影響到你的測試策略。

在RF接收測試期間,測試工程師的主要目標還與DigRF以前相同,即捕獲I/Q信息,對獲得的數據集執行定制的數字信號處理算法,并記錄參數化結果,以確定設備是否合格。但與前代RFIC相比較,DigRF器件可能給生產測試增加大量開銷。尋找盡可能減少這種開銷的方式,就成為工程師在設計自動化生產測試系統時所面臨的主要挑戰。

理解接口

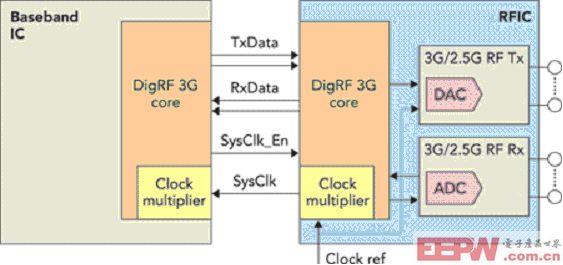

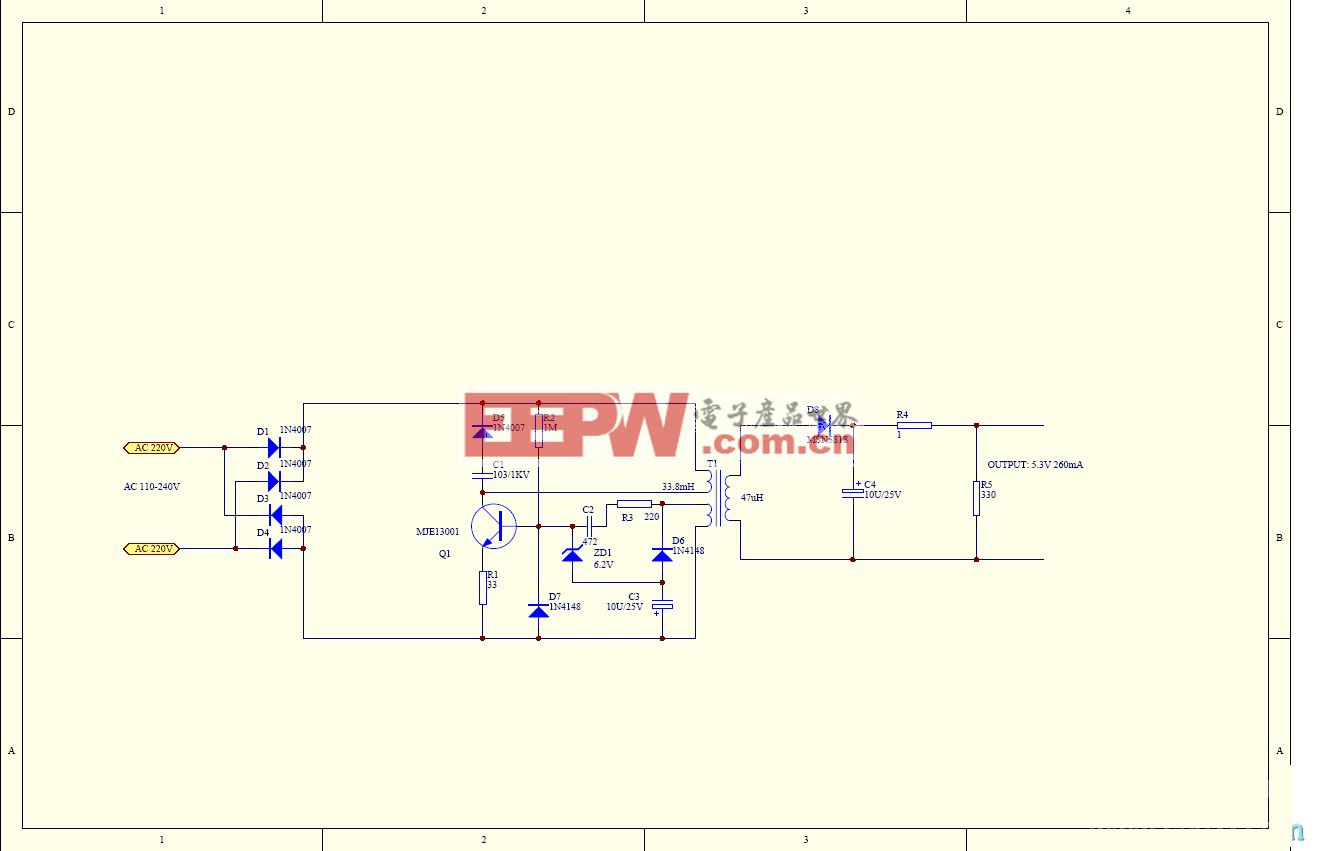

DigRF 3G定義了實現接口所需要的最小信號數;一個基本的手機配置只需要6根線(圖1)。RxData/TxData信號在一個分組協議中傳送I/Q數據以及控制與狀態消息的數字表示。

圖1. 基本的DigRF手機配置只需要6根線。

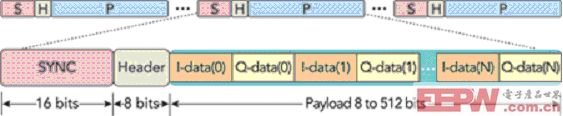

以DigRF信號傳輸的數據被封裝在協議包或稱幀內。每個幀都包括三部分:同步(sync),頭(header),與有效載荷(payload)(圖2)。每個包的開始都有相同的16 bit同步序列,數字接收電路用它對每個幀做實時選通相位的對準。

接下來的8個位是頭,它定義有效載荷的作用與內容。頭本身由三部分構成:3位表示有效載荷的大小,4位描述LCT(邏輯信道類型),1位表示CTS(清除發送)信號。

圖 2. DigRF 3G數據幀開始于一個16 bit同步序列,后面是一個8 bit頭和I、Q數據。

不同數據包的有效載荷部分有大小變化,從而產生不同級別的編碼開銷。LCT定義了有效載荷中包含的內容,以及可分類為控制數據或I/Q數據的內容。CTS允許在RF發射期間,由RF設備控制來自基帶的數據流。

幀中余下的N位就包含了要傳輸的實際數據。例如,在DigRF 3G的非分集模式下,RxData幀將使用數據信道C和256 bit有效載荷,包含8 bit的交替I數據和Q數據。

DigRF 3G支持數字傳輸下的三種時序模式,具體取決于被傳輸RF信息的類型(表1)。DigRF標準還支持三種公共的輸入基準時鐘頻率(19.0 MHz、26.0 MHz和38.4 MHz);時鐘通過SysClk信號送至基帶。與速度模式無關,DigRF處理器會用一個本地的FIFO緩沖管理數據流,當傳輸幀時會產生一個無法預測的時序。

生產測試的挑戰

對采用DigRF協議器件作成功測試的關鍵是要找到一種方式,能在RF接收測試期間管控RxData包的不確定性狀態。在對DigRF產品作RF接收測試期間,能觀察到RxData信號合成狀態的多級不確定性:

?相位時序;

?幀時序;

?幀類型;

?有效載荷中的數據。

312 Mbps的數據速率來自于一個1248 MHz主時鐘(一般由PLL生成)的1/4分頻器。在生產性測試系統中,考慮到影響RF前端的相位噪聲性能的重要性,器件的時鐘輸入應由RF儀器提供。與普通數字子系統相比較,這個時鐘源的起始相位通常是不可控的。DUT(待測設備)的輸入時鐘相位未定,PLL倍頻器/分頻器產生的相位也不確定,兩者結合導致RxData輸出時序無法預測,包括器件各上電循環之間,以及多地點并行測試配置中的不同器件之間的輸出時序。

一種生產型測試儀應有這種能力,即在各次測試間對測試儀硬件和DUT作必要修改時,仍保持數字子系統的運行。它使測試儀能夠維持相對于DUT輸出的選通時序,避免在正式運行中的選通相位重調,節省了測試時間。

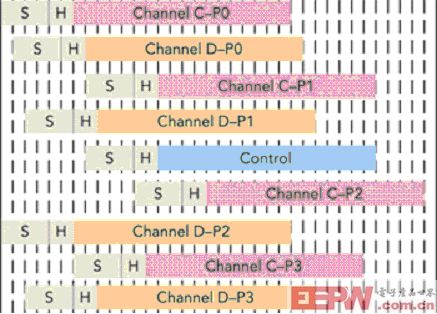

下一個重要的測試挑戰是尋找一個能處理多級不確定性數據包傳輸性能的方式。如圖3所示,在DUT的每個RF接收測試期間,測試儀都不知道每個包會在哪個測試循環中傳輸,包的類型會是什么,或者包的類型是否符合預期(例如,RFIC會生成一個主動的控制狀態消息)。

圖 3. 由于數據包的不確定性,在一款器件的每次RF接收測試期間,測試儀不知道每個包會在哪個測試循環中傳輸,包的類型是什么,或者包的類型是否符合預期。

評論