采用抗混疊濾波器的高性能、12位、500 MSPS寬帶接收機

濾波器和接口設計程序

為實現最佳性能(帶寬、SNR、SFDR等),放大器和ADC應對一般電路形成一定設計限制:

放大器應參考數據手冊推薦的正確直流負載,以獲得最佳性能。

放大器與濾波器的負載間必須使用正確數量的串聯電阻。這是為了防止通帶內的不需要的峰值。

ADC的輸入應通過外部并聯電阻降低,并使用正確串聯電阻將ADC與濾波器隔離開。此串聯電阻也會減少峰值。

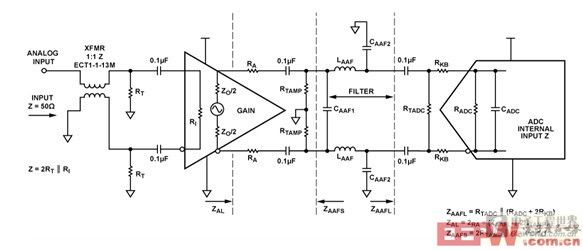

圖5所示的一般電路適用于大多數高速差分放大器/ADC接口,將作為本文的討論基礎。此設計方法傾向于利用大多數高速ADC的相對較高輸入阻抗和驅動源(放大器)的相對較低阻抗,將濾波器的插入損耗降至最低。

圖5. 采用低通濾波器的一般差分放大器/ADC接口

基本設計流程如下:

選擇外部ADC端接電阻RTADC,使得RTADC與RADC的并聯組合介于200 Ω和400 Ω之間

根據經驗和/或ADC數據手冊建議選擇RKB,通常介于5 Ω和36 Ω之間。

使用下式計算濾波器負載阻抗:

ZAAFL= RTADC|| (RADC+ 2RKB)

S選擇放大器外部串聯電阻RA。如果放大器差分輸出阻抗在100 Ω至200 Ω范圍內,RA應小于10 Ω。如果放大器輸出阻抗為12 Ω或更低,RA應介于5 Ω和36 Ω之間。

選擇RTAMP,使放大器獲得的總負載ZAL最適合通過以下公式選擇的特定差分放大器:

ZAL= 2RA+ (ZAAFL|| 2RTAMP)

計算濾波器源阻抗

ZAAFS= 2RTAMP|| (ZO+ 2RA)

使用濾波器設計程序或表,利用源阻抗、負載阻抗、ZAAFS和ZAAFL、濾波器類型、帶寬、階次等設計濾波器。帶寬比采樣速率的一半高出約40%,以確保直流至fs/2頻率范圍內的平坦度。

內部ADC電容CADC應從程序生成的最終分流電容值減去。程序將給出差分分流電容值CSHUNT2。最終共模分流電容為:

CAAF2= 2(CSHUNT2– CADC)

經過上述初步計算,應了解電路的下列項目。

CAAF2值應至少為10 pF,比CADC大數倍。這樣可將濾波器對CADC波動的敏感度降至最低。

ZAAFL與ZAAFS之比不應高于約7,使濾波器在大多數濾波器表和設計程序的限值內

CAAF1值應至少為5 pF,以盡可能降低對寄生電容和元件波動的敏感度。

電感LAAF應為合理值,至少為數nH。

在某些情況下,濾波器設計程序可提供一個以上獨特解決方案,特別是對于更高階濾波器。應始終選擇采用最合理元件值組合的解決方案。另外應選擇結束于分流電容的配置,以便分流電容與ADC輸入電容組合。

電路優化技術和權衡

本接口電路內的參數具有高互動性;因此優化電路的所有關鍵規格(帶寬、帶寬平坦度、SNR、SFDR、增益等)幾乎不可能。不過,通過變更RA和RKB,可以最大程度地減少通常發生于帶寬響應內的尖峰。

通帶內的尖峰隨輸出串聯電阻RA值增加而降低。然而,此電阻值增加時,信號衰減也會增加,放大器必須驅動更大信號才能填充ADC的滿量程輸入范圍。

RA值也會影響SNR性能。更大值在降低帶寬峰化的同時傾向略微提高SNR,因為驅動ADC滿量程需要更高信號電平。

ADC輸入端的RKB串聯電阻應選擇為盡量減少任何殘余電荷注入(從ADC內部采樣電容)造成的失真。增加此電阻也傾向減小帶內尖峰。

不過,增加RKB會增加信號衰減,因此放大器必須驅動更大信號才能填充ADC的輸入范圍。

優化通帶平坦度的另一方法是略微變更濾波器分流電容CAAF2。

ADC輸入端接電阻RTADC通常應選擇為使凈ADC輸入阻抗介于200 Ω和400 Ω之間。降低該電阻可減少ADC輸入電容的效應并穩定濾波器設計,但會增加電路的插入損耗。提高該值也會減小峰值。

上述因素的權衡可能有些困難。本設計中,每個參數權重相等;因此所選值代表了所有設計特征的接口性能。某些設計中,可根據系統要求選擇不同值,以優化SFDR、SNR或輸入驅動電平。

請注意,本設計中的信號與0.1 μF電容進行交流耦合,以阻擋放大器、其端接電阻和ADC輸入之間的共模電壓。共模電壓的詳情請參見AD9434數據手冊。

無源元件和PCB寄生考慮因素

該電路或任何高速電路的性能都高度依賴于適當的PCB布局,包括但不限于電源旁路、受控阻抗線路(如需要)、元件布局、信號布線以及電源層和接地層。高速ADC和放大器PCB布局的詳情請參見教程MT-031和教程MT-101。

低寄生表面貼裝電容、電感和電阻應用于濾波器內的無源元件。所選電感來自Coilcraft 0603CS系列。濾波器所用表面貼裝電容的穩定性和精度是5%、C0G、0402型。

系統的完整文檔請參見CN-0238設計支持包(www.analog.com/ CN0238-DesignSupport)

常見變化

對于需要更少帶寬、更高雜散性能和更低功耗的應用,可使用ADA4927-1/ADA4927-2或ADA4938-1/ADA4938-2。ADA4927-1帶寬為2.3 GHz,僅使用20 mA的電流,而ADA4938-1帶寬為1.0 GHz,使用37 mA的電流。

對于需要更低分辨率的應用,8位、500 MSPSAD9484與AD9434引腳兼容。AD9484在250 MHz模擬輸入頻率下的SNR為47 dBFS。

對于需要更低采樣速率的應用,12位、170 MSPS/210 MSPS/250 MSPSAD9230是與AD9434引腳兼容的ADC,且具有大致相同的動態性能。

對于需要數字預失真(DPD)觀測的應用,也可考慮12位、500 MSPSAD6641該產品具有片內16k × 12位FIFO。

電路評估與測試

此電路使用經過修改的AD9434-500EBZ電路板和HSC-ADC-EVALCZFPGA數據采集板。這兩片板具有對接高速連接器,可以快速完成設置并評估電路性能。經過修改的AD9434-500EBZ板包含依照本筆記所述進行評估的電路,HSC-ADC-EVALCZ數據采集板配合Visual Analog評估軟件和SPI控制器軟件使用,以正確控制ADC并采集數據。AD9434-500EBZ板的原理圖、BOM和布局請參見用戶指南UG-290。CN-0238設計支持包中的“readme.txt”文件(www.analog.com/CN0238-DesignSupport)說明了對標準AD9434-500EBZ板做出的修改。應用筆記AN-835詳細說明了如何設置硬件和軟件,以運行本電路筆記所述的測試。

評論