基于FPGA的高速數(shù)據采集系統(tǒng)設計

在adc.v模塊中,需要完成FPGA對TLV1572的接口邏輯代碼的設計,其實質就是在TLV1572的時序分析的基礎上來設計邏輯代碼,使得FPGA能夠按照其時序要求完成對A/D芯片的各種控制,包括提供給TLV1572的串行時鐘信號信號ADC_CLK、CS片選信號ADC_CSn以及從TLV1572中讀取出轉換完成的串行數(shù)據S_DATA。

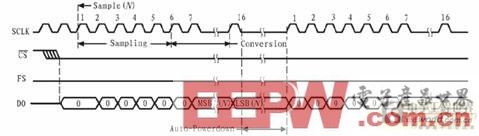

TLV1572的時序圖如圖5所示。

圖5 TLV1572的時序圖

從時序圖可見,A/D芯片的轉化過程是在當CS為低電平后,由SCLK的上升沿發(fā)起的,輸出的頭六位二進制數(shù)字均為“0”,此時A/D芯片正處于采樣階段,數(shù)字無效,這六位無效的二進制數(shù)之后,A/D轉換完成后的二進制數(shù)據在SCLK的上升沿被送到總線上,這時,作為系統(tǒng)主控制芯片的FPGA應當去采樣總線上的數(shù)據,得到轉換后的結果。

2.2 FPGA控制USB2.0芯片的軟件設計

在usb.v模塊中,需要完成FPGA對CY7C68013A的接口邏輯代碼的設計和異步FIFO模塊的設計。其中,對CY7C68013A的接口邏輯代碼主要是完成對CY7C68013A芯片的端點FIFO的各種控制,包括16位的數(shù)據信號FIFO_DATA[15:0]、2位端點FIFO選擇信號FIFO_ADDR[1:0]、端點FI-FO滿標志位信號FIFO_Full、端點FIFO寫使能信號FIFO_WR_en。因為adc.v模塊和芯片外部的CY7C68013A工作在不同的時鐘域內,故異步FIFO模塊設計部分設計的目的除了是要完成從ade.v模塊讀取過來數(shù)據的緩沖,另外就是需要解決異步時鐘域數(shù)據傳輸可能出現(xiàn)的亞穩(wěn)態(tài)問題。

具體來說,F(xiàn)PGA在工作時需要不斷向CY7C68013A的端點FIFO寫入數(shù)據,而FPGA與CY7C68013A之間的工作模式屬于同步方式,兩者都由PLL _2模塊提供40 MHz的時鐘信號進行工作,那么它們之間的關系就是同步Slave FIFO的寫操作,由FPGA向CYTC68013A中寫入數(shù)據。

在Verilog HDL程序設計中,需要設計一個狀態(tài)機來完成同步Slave FIFO寫的時序,寫時序如下;1)IDLE:當寫事件發(fā)生時,進狀態(tài)1;2)狀態(tài)1:使FIFOADR[1:0]指向IN FIFO,進狀態(tài)2;3)狀態(tài)2:如果端點FIFO滿,在當前狀態(tài)等待,否則進狀態(tài)3;4)狀態(tài)3:驅動數(shù)據到數(shù)據線上,使SLWR有效,持續(xù)一個IFCLK周期,進狀態(tài)4;5)狀態(tài)4:如需傳輸更多的數(shù),進狀態(tài)2,否則進入IDLE狀態(tài)。

該狀態(tài)轉換的狀態(tài)圖如圖6所示。

圖6 狀態(tài)轉換的狀態(tài)圖

2.3 FPGA的頂層模塊的設計

由圖4可知,top.v模塊是FPGA整個系統(tǒng)的頂層模塊,它通過頂層調用的方式把adc.v和usb.v兩個模塊組合成一個完整的系統(tǒng),系統(tǒng)與外界進行通信是通過top.v這個模塊對外的各個接口來實現(xiàn)的,具體到器件層面,就表現(xiàn)為由top.v文件定義的FPGA的相關的管腳來和A/D與USB2.0芯片進行數(shù)據的交換、控制信息以及時鐘信號的傳遞。這種自頂向下的設計方法,不僅符合人的思維邏輯,也大大地簡化了大規(guī)模邏輯電路的設計工作,使人們從繁瑣的自底向上的底層設計中解放出來,以一種系統(tǒng)級的思維模式設計電路。這是自頂向下設計方法的巨大優(yōu)勢之一。頂層top.v模塊是通過例化的方式來調用adc.v模塊和usb.v模塊的以及PLL模塊。

2.4 USB2.0芯片的固件程序設計

在USB的體系中,無論是其本身的規(guī)范還是各種廠家所提供的芯片資料,關于主機對USB的檢測都稱之為枚舉Enumeration(and ReNumer-ation),即枚舉(與重新枚舉)。固件在這發(fā)揮了無法替代的作用。應該說所有基于微控制器及其外圍電路的功能設備的正常工作都離不開固件的參與,固件的作用就是輔助硬件,或者說是控制硬件來完成預期的設備功能。沒有固件的參與和控制,硬件設備只是芯片的簡單堆砌,無法實現(xiàn)預期的功能。

CY7C68013A內部集成了增強型的8051內核,它與8051指令集二進制是兼容的,那么就可以選擇匯編或者高級語言C51來編寫固件代碼,兩者各有優(yōu)缺點,適用的環(huán)境也不同。本設計中采用C51來編寫固件程序,關于開發(fā)C51語言的Keil μVision 2開發(fā)編譯環(huán)境在此不再贅述。

Cypress公司為了簡化和加速用戶使用CY7C68013A芯片進行USB外設的開發(fā)過程,特別設計了一個完整的固件程序的框架。這個框架可以執(zhí)行CY7C68013A芯片的初始化、USB標準設備請求的處理和USB掛起電源管理服務。用戶只需要提供一個USB描述符表,添加其他端點接收和發(fā)送數(shù)據的通信代碼,以及控制外圍電路的程序代碼。

在Keil μVision 2集成開發(fā)環(huán)境下,新建工程后,需要將工程代碼復制到工程目錄中并添加至工程列表中,開發(fā)固件程序需要幾個重要的文件依次為:1)fw.c,框架程序的代碼。2)periph.c,用戶函數(shù)掛鉤的相關定義,外圍設備的控制文件。在上節(jié)中,主程序fw.c調用的TD_lnit()函數(shù)即在此定義出來。3)dscr.a51,USB描述符表,上節(jié)中關于描述符的定義在這個文件中給出。4)EZUSB.lib,EZ-USB函數(shù)庫目標代碼。5)USBJmpTb.OBJ,EZ-USB中斷向量和跳轉表。6)FX2.h,程序運行所需要的一些宏定義。7)fx2regs.h,CY7C68013A相關的寄存器定義及位屏蔽的宏定義。8)syncdly.h,定義了若干延時函數(shù)供程序調用。

3 Modelsim環(huán)境下仿真與結果

ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述語言的仿真軟件,該軟件可以用來實現(xiàn)對設計的VBDL、Verilog HDL或是兩種語言混合的程序進行仿真,同時也支持IEEE常見的各種硬件描述語言標準。

目前需要對adc.v模塊進行功能仿真,以此驗證該模塊的功能的正確性。仿真測試的方法就是給adc.v這個模塊的s_data數(shù)據輸入端,即A/D芯片的串行數(shù)據的輸出端,加載一組測試數(shù)據,每16個為一組測試數(shù)據,模擬在真實環(huán)境下從A/D芯片讀取出來的二進制數(shù)據,然后在adc.v模塊的輸出端,即并行的16位寬的data_out端口觀察是否與給定的測試數(shù)據相一致。假如一致,則模塊的功能是正確的。假如有個別位的數(shù)據不一致,則需要檢查模塊的代碼是否存在問題。在編輯器中編寫Testbench程序如下(非關鍵的程序限于篇幅,就省略了):

由上面的程序可以看見,給s_data端加載的一組16位二進制數(shù)據為“0000-0011_0110_1011”。在ModelSim環(huán)境下,將待測試的文件與該測試文件放在同一個工程下,設置好相關參數(shù)后運行仿真可以得到如下仿真波形,如圖7所示。

鎖相環(huán)相關文章:鎖相環(huán)原理

評論