基于FPGA的高速數據采集系統設計

隨著嵌入式技術的飛速發展,對嵌入式系統的應用需求也呈現出不斷增長的態勢,因此,嵌入式技術也相應地取得了重要的進展,系統設備不斷向高速化、集成化、低功耗的方向發展。現場可編程門陣列FPGA經過近20年的發展,到目前已成為實現數字系統的主流平臺之一。 FPGA具有單片機和DSP無法比擬的優勢,相對于單片機和DSP工作需要依靠其上運行的軟件進行,FPGA全部的控制邏輯是由延時更小的硬件來完成的。

本文引用地址:http://www.104case.com/article/247519.htm通用串行總線(USB)是現代數據傳輸的發展趨勢,是解決計算機與外設連接瓶頸的有效手段,USB2.O版本在原先的版本基礎上實現許多技術上的飛躍與進步。USB2.0協議規范有以下主要優點:1)速度快,接口的傳輸速度高達480Mh/s,遠大于PCI接口的132 Mb/s的傳輸速度;2)連接簡單,所有的USB外設利用通用的電纜可簡單方便地連入PC機中,安裝過程高度自動化;3)支持多設備連接,USB接口支持多個不同設備采用“級聯”方式來連接外設。

故為了將數據采集系統設計更加符合高速化和集成化的趨勢,采用了FPGA和USB2.0組合的方案來進行。

1 數據采集系統的框架與硬件設計方案

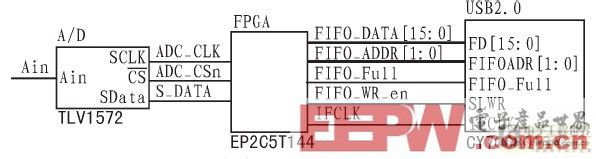

系統硬件設計部分中,在完成系統時鐘源、電源等必要電路的設計基礎上,重點就是完成系統內各個部件的接口電路的設計,通過這部分的設計,基本的硬件平臺就建立起來了。系統部件間的硬件電路接口設計如圖1所示。

圖1 系統部件間的硬件電路接口設計

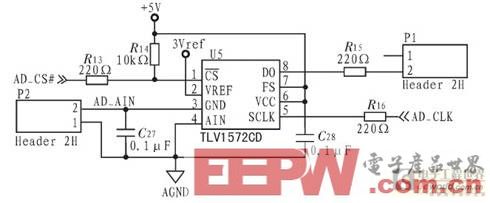

A/D芯片在此選用了德州儀器公司的10位串行接口芯片TLV1572,8管腳的SOIC封裝,它外部較少的管腳不僅能夠很方便地實現與其他器件連接,而且它體積小,可以節省很多布線資源,如圖2所示。TLV1572的最高采樣速率為1.25 MS/s,其積分非線性誤差INL<±1LSB,可以采用3 V或5 V的供電方式。

圖2 A/D芯片及周邊電路

由于大部分USB1.1的芯片都需要微控制器參與數據從端點FIFO到應用環境的轉移,微控制器在里面扮演了搬運者的角色,那么顯然微控制器本身的工作頻率就極大地限制了數據傳輸帶寬的進一步提高,微控制器將成為制約整個系統速度提高的瓶頸。

故在此選用的是Cypress Semiconductor公司的EZ-USBFX2(CY7C68013A)USB2.0芯片,它集成了USB2.0收發器,串行接口引擎SIE和可編程的外圍接口。該芯片的另一大優點就是提供了一種獨特架構,使USB接口和應用環境直接共享Slave FIFOs,微控制器無需參與數據傳輸,這樣就極大地提高了系統數據傳輸速率,如圖3所示。

圖3 EZ-USB FX2芯片的內部結構

由于FPGA的I/O管腳數目眾多,它在和A/D芯片及USB2.0芯片相連時,能夠按照優化布線資源的方式進行PCB布局設計,具體的連接方法在圖1中已經給出。

2 數據采集系統軟件設計方案

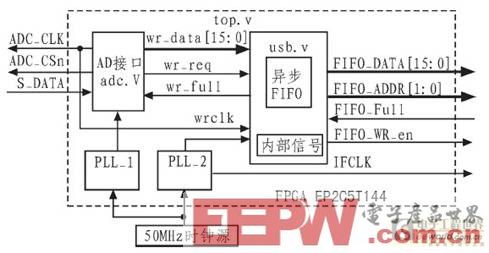

FPGA軟件設計方案中采用了自頂向下的設計方法,運用Verilog HDL語言來設計數字系統,分別完成數字系統內部各個子模塊的設計。數據采集系統結構及模塊間的連接示意圖如圖4所示。

圖4 數據采集系統結構及模塊間的連接示意圖

由圖4可見,系統主要由3個模塊組成。它們分別是A/D接口adc.v模塊、USB接口usb.v模塊以及頂層top.v模塊,其中在頂層top.v模塊中,完成了對其他兩個模塊的調用,使它們拼接成為一個完整的系統。其中鎖相環PLL_1和PLL_2分別給ade.v模塊和usb.v模塊提供時鐘源。

鎖相環相關文章:鎖相環原理

評論