一種使用Cadence PI對PCB電源完整性的分析方法

2.2 電源完整性仿真

本文引用地址:http://www.104case.com/article/246386.htm2.2.1 單節(jié)點仿真,分析驗證并優(yōu)化電容選擇

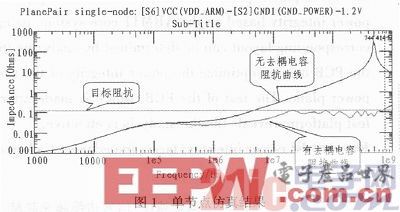

在單節(jié)點仿真中,忽略電源系統(tǒng)中各元件實際的物理連接,假設(shè)電源調(diào)壓模塊VRM、仿真激勵源、電流源和所有電容都并聯(lián)在一起,單結(jié)點仿真可以得到維持目標(biāo)阻抗所需要的電容。VDD_ARM電源網(wǎng)絡(luò)單節(jié)點仿真結(jié)果如圖1所示,所有電容有效時(下面曲線)和所有電容無效(上面曲線)電源分配系統(tǒng)的阻抗,目標(biāo)阻抗(中間直線)。最后選擇0603貼片封裝,150 pF電容4個,390 pF電容3個,0.1μF電容3個,4.7μF電容2個。

2.2.2 多節(jié)點仿真,放置去耦電容優(yōu)化布局

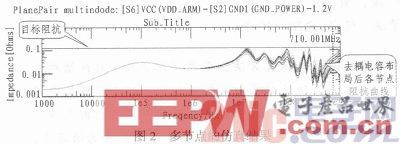

由于單節(jié)點仿真沒有考慮去耦電容的布局,為了獲得更精確的結(jié)果,考慮噪聲源和去耦電容的放置位置,在全頻率范圍內(nèi)進(jìn)行多節(jié)點仿真。在多節(jié)點仿真時,Cadence PI根據(jù)用戶定義將電源平面分隔成多個網(wǎng)格,并對每一個網(wǎng)格進(jìn)行建模,然后將放置的去耦電容、電壓調(diào)節(jié)模塊VRM和噪聲源與具體的網(wǎng)格點連接起來,產(chǎn)生每一個節(jié)點的頻率-阻抗仿真波形。

為獲得較高的精確度,網(wǎng)格尺寸大小必須大于系統(tǒng)最高頻率對應(yīng)波長的1/10。波長計算如式(3):

本系統(tǒng)最高頻率為667 MHz,電路板材料是FR-4,介電常數(shù)為εr=4.5。由式(3)計算得到λ為212.033 mm。VDD_ARM電源平面為80 mm×70 mm,選擇44可精確分析,為了便于分析,本文選擇88的網(wǎng)格。放置電容時,電容的有效去耦半徑是一個比較重要的參數(shù),根據(jù)經(jīng)驗數(shù)據(jù),這一半徑在實際應(yīng)用中的取值最好小于λ/50。不斷進(jìn)行多節(jié)點仿真,使得所擺放的電容數(shù)目最小化。圖2為VDD_ARM/地平面對多節(jié)點的仿真結(jié)果。從結(jié)果可知,在放置相應(yīng)的去耦電容之后,除極個別點外,平面阻抗在小于710 MHz的范圍內(nèi)都是小于目標(biāo)阻抗的,而ARM11核心系統(tǒng)的最高時鐘頻率為667MHz,因此此次去耦電容的布局完全滿足要求。

2.2.3 電源平面靜態(tài)IR-Drop直流壓降分析

芯片要正常工作需將供電電壓限定在允許的波動范圍之內(nèi)。電源波動是由DC損耗和AC噪聲兩部分造成的,直流壓降DC IR-Drop是產(chǎn)生DC損耗的主要原因。靜態(tài)IR-Drop直流壓降主要與金屬連線的寬度及所用層、該路徑所流過的電流大小、過孔的個數(shù)和位置有關(guān)。在Cadence PI中設(shè)置電源供給管腳和灌電流后,對布局布線完成后的ARM11核心供電電壓網(wǎng)絡(luò)VDD_ARM進(jìn)行直流壓降分析,當(dāng)ARM11核心系統(tǒng)工作頻率為667 MHz時,其1.2 V的直流電壓的允許波動幅度為+/-0.05 V。Cadence PI仿真軟件計算出VDD_ARM網(wǎng)絡(luò)電壓梯度,其中Drop的最大值為0.013 V,小于允許波動的幅度為+/-0.05 V,完全滿足S3C6410工作電壓要求,可以保證系統(tǒng)工作的穩(wěn)定性。

2.2.4 電源平面電流密度分析

當(dāng)電源平面上過孔過多或者分布不合理時,會出現(xiàn)電流流過狹窄區(qū)域,從而造成該區(qū)域電流密度過大。電源平面上最大的電流密度區(qū)域稱之為熱點,熱點有可能會導(dǎo)致嚴(yán)重的熱穩(wěn)定性問題,因此要合理地設(shè)計過孔,使板的電流密度分布均勻,避免在關(guān)鍵芯片和高速走線附近出現(xiàn)熱點。圖3為VDD_ARM網(wǎng)絡(luò)電流密度分布,圖中標(biāo)注點為該平面熱點,其位置周圍為一塊空白區(qū)域,平面其他部分電流密度較均勻。

3 PCB電源完整性測試

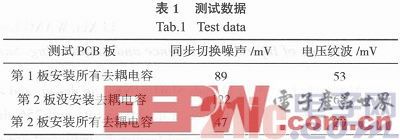

在第1版PCB中,沒有利用Cadence PI分析,只是根據(jù)經(jīng)驗放置了一些去耦電容。在調(diào)試時,發(fā)現(xiàn)高速數(shù)字信號的波形不好,有時會有誤碼。在第2版中,通過Cadence PI進(jìn)行分析,對去耦電容的數(shù)值數(shù)量和位置,部分原件的布局布線進(jìn)行了調(diào)整。

利用動態(tài)電子負(fù)載模擬高速電子線路中多芯片同時切換時所造成的系統(tǒng)供電電流的高速周期性突變,對ARM11核心系統(tǒng)的PCB板搭建如圖4所示的測試平臺,分別對第1版安裝了去耦電容PCB,第2板沒安裝去耦電容和第2板安裝了去耦電容的VDD_ARM/地電源平面對進(jìn)行測試。

開關(guān)電源1.2 V為電源平面提供0_2~0.8A左右的輸出電流,動態(tài)負(fù)載在恒壓的情況下,輸出阻抗周期變化,電流幅度可完成同周期的0.2~0.8 A的跳變,測試數(shù)據(jù)如表1。從數(shù)據(jù)可看出經(jīng)過Cadence PI分析后生產(chǎn)的第2版PCB的電源完整性得到較大幅度的改善。

4 結(jié)論

經(jīng)過Cadence PI的仿真分析后,制作出ARM11核心系統(tǒng)PCB板,通過電路實際測量,發(fā)現(xiàn)各電源分配系統(tǒng)均能很好工作,與仿真結(jié)果基本一致。隨著系統(tǒng)頻率高速增加,電源分配系統(tǒng)復(fù)雜化,工程生產(chǎn)成本和周期的嚴(yán)格控制,在設(shè)計電子系統(tǒng)時,于系統(tǒng)層面進(jìn)行電源完整性仿真分析、模擬真實系統(tǒng)的行為,對提高設(shè)計效率、減少設(shè)計誤差很有必要。

電容相關(guān)文章:電容原理 電容傳感器相關(guān)文章:電容傳感器原理

評論