基于FPGA和CAN總線的飛行模擬器通信接口設(shè)計(jì)

摘要:在飛行模擬器的設(shè)計(jì)中,為了使數(shù)據(jù)能夠快速有效地在飛行模擬器的各個(gè)模塊之間進(jìn)行高速傳遞,提出了一種使用FPGA作為CAN總線節(jié)點(diǎn)結(jié)構(gòu)中的核心處理器的設(shè)計(jì)方法,并完成了飛行模擬器通信接口的軟硬件設(shè)計(jì)。采用Verilog HDL進(jìn)行編程,能夠完成對(duì)SJA1000總線控制器的有效讀寫。實(shí)際測(cè)試表明,相較于單片機(jī)作為處理器,本設(shè)計(jì)可擴(kuò)展性好,易于修改和移植,能降低模擬器成本。

本文引用地址:http://www.104case.com/article/246384.htm飛行模擬器是現(xiàn)代飛行員訓(xùn)練的必需設(shè)備,它是一種由計(jì)算機(jī)實(shí)時(shí)控制、多系統(tǒng)協(xié)調(diào)工作、能模擬真實(shí)飛行環(huán)境的模擬設(shè)備。相較于利用飛機(jī)的飛行訓(xùn)練而言,利用飛行模擬器的模擬飛行訓(xùn)練不僅不受天氣等自然條件的制約,而且沒有后勤、機(jī)務(wù)保障以及飛行安全等因素的限制。國(guó)內(nèi)外許多單位均研制了各種不同種類和規(guī)模的訓(xùn)練模擬器,并取得良好的訓(xùn)練效果,保證了飛行任務(wù)的圓滿完成。

在飛行模擬器的設(shè)計(jì)中,要求大量的信息能夠快速有效地在飛行模擬器的各個(gè)模塊之間進(jìn)行高速傳遞,這就需要一定的通信接口協(xié)議來(lái)實(shí)現(xiàn)數(shù)據(jù)的交互。目前,飛行模擬器通常采用CAN總線作為通信協(xié)議,并采用單片機(jī)作為微處理器,可擴(kuò)展性差。文章根據(jù)飛行模擬器的結(jié)構(gòu)特點(diǎn),分析了現(xiàn)場(chǎng)總線技術(shù)和FPGA技術(shù)的發(fā)展,根據(jù)飛行模擬器的實(shí)際需要和總線自身特點(diǎn),選用了CAN總線來(lái)作為主機(jī)和現(xiàn)場(chǎng)設(shè)備的通信方式,并使用FPGA作為CAN總線節(jié)點(diǎn)結(jié)構(gòu)中的核心處理器,對(duì)飛行模擬器通信接口進(jìn)行了設(shè)計(jì)。

1 硬件系統(tǒng)設(shè)計(jì)

CAN(Controller Area Network)總線是一種串行通信總線,是國(guó)際上應(yīng)用最廣泛的開放式現(xiàn)場(chǎng)總線之一。CAN最早被設(shè)計(jì)作為汽車環(huán)境中微控制器的通訊,但由于其靈活性好、可靠性高、功能完善,已經(jīng)被廣泛應(yīng)用到各個(gè)自動(dòng)控制領(lǐng)域,CAN總線具有根據(jù)優(yōu)先級(jí)的多主結(jié)構(gòu)、可靠的錯(cuò)誤檢測(cè)和處理機(jī)制、傳輸速率高(最高可達(dá)1 Mb/s)、傳輸距離遠(yuǎn)(波特率低于5 kb/s時(shí)最遠(yuǎn)可達(dá)10 km),克服了RS-485網(wǎng)絡(luò)的低總線利用率、單主從結(jié)構(gòu)、無(wú)硬件錯(cuò)誤檢測(cè)的不足。在飛行模擬器的設(shè)計(jì)過(guò)程中,主控機(jī)需要與多個(gè)模塊進(jìn)行交互,選用CAN總線接口是非常適合的。

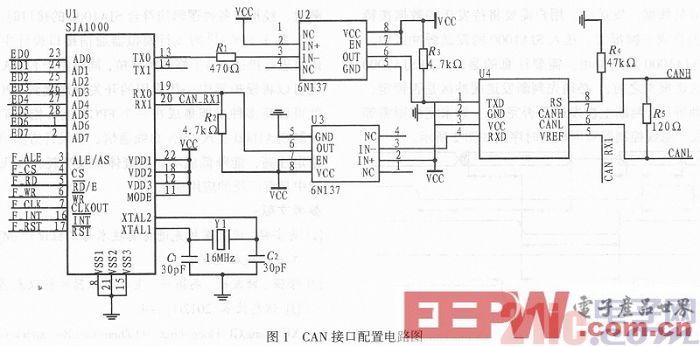

飛行模擬器通信接口的硬件設(shè)計(jì),以CAN總線作為通信協(xié)議,選用ALTERA公司CYCLONE系列EP1C6Q240C8作為CAN節(jié)點(diǎn)的核心處理器,采用Philips公司的SJA1000T作為CAN總線控制器,在CAN總線控制器與CAN物理總線之間選用PCA82C250作為CAN收發(fā)器,為了增強(qiáng)抗干擾能力,

保護(hù)CAN總線控制器,在SJA1000T與PCA82C250之間使用6N137進(jìn)行光電隔離,其速度為10 MHz。在Quartus II軟件中運(yùn)用Verilog對(duì)FPGA編程,實(shí)現(xiàn)對(duì)SJA1000T的控制及CAN節(jié)點(diǎn)之間的通信功能。接口電路設(shè)計(jì)如圖1所示。

SJA1000芯片是一款獨(dú)立的CAN總線控制器,相對(duì)于它的前一款PCA82C200,SJA1000是在原有的BasicCAN模式的基礎(chǔ)上增加了PeliCAN模式,這種模式能夠支持CAN2.0B協(xié)議。為了提高SJA1000的總線驅(qū)動(dòng)能力,在SJA1000與CAN總線之間加入了PCA82C250總線收發(fā)器,其主要功能是增大通信距離,提高系統(tǒng)的瞬間抗干擾能力,保護(hù)總線,降低射頻干擾,實(shí)現(xiàn)熱防護(hù)等。

系統(tǒng)設(shè)計(jì)中選用FPGA作為CAN總線節(jié)點(diǎn)的核心處理器,能夠在速度和體積上有更好的適應(yīng)性,可以增強(qiáng)飛行模擬器通信接口設(shè)計(jì)的靈活性和可擴(kuò)展性,因?yàn)樵陲w行模擬器設(shè)計(jì)中,有時(shí)還需要用到其他通信接口,比如括RS232和RS422。EP1C6Q240是ALTERA公司推出的一款高性價(jià)比的FPGA,工作電壓為3.3 V,內(nèi)核電壓1.5 V,采用0.13μm工藝技術(shù),其內(nèi)部具有5 980個(gè)LEs,含有20個(gè)MK4 RAM塊(128×36 bits),總的RAM空間共計(jì)92 160比特,內(nèi)嵌2個(gè)鎖相環(huán)電路,最大用戶I/O為185個(gè),配置芯片選用EPCS1,對(duì)于FPGA的下載方式,通常可以采用JTAG方式和AS方式,不同下載方式,其硬件連接方式不用。JTAG方式,下載程序到FPGA芯片內(nèi)RAM中,F(xiàn)PGA芯片內(nèi)的程序掉電后無(wú)法保存,JTAG下載方式適合調(diào)試程序時(shí)使用,而AS方式則能將程序下載到配置芯片內(nèi),配置芯片內(nèi)的程序掉電后也可以保存,再次上電后自動(dòng)裝載到FPGA內(nèi)并由FPGA開始運(yùn)行。

在CAN總線接口硬件設(shè)計(jì)中,主要是CAN總線控制器與FPGA以及CAN總線控制器與CAN總線收發(fā)器之間的接口電路設(shè)計(jì)。在設(shè)計(jì)時(shí),相比于采用單片機(jī)作為微處理器的設(shè)計(jì),F(xiàn)PGA具有豐富的I/O端口,為了使FPGA的3.3V I/O接口電平與SJA1000的5 V TTL電平標(biāo)準(zhǔn)相匹配,在FPGA與SJA1000連接時(shí)需要使用74ALVC164245電平轉(zhuǎn)換器,這樣CAN總線控制器SJA1000的AD0~AD7、片選信號(hào)CS、RD、WR、ALE、INT、MODE分別經(jīng)過(guò)電平轉(zhuǎn)換器再與FPGA的I/O相連。為了增強(qiáng)抗干擾能力,總線控制器SJA1000的發(fā)送輸出端TX0與接收輸入端RX0分別經(jīng)集成光電耦合器6N137,與總線收發(fā)器PCA82C250的TXD和RXD相連,PCA82C250的CANH、CANL端口直接與CAN物理總線相連。PCA82C250是CAN總線控制器和物理總線之間的接口,具有可向總線差動(dòng)發(fā)送數(shù)據(jù)和從CAN總線控制器差動(dòng)接收數(shù)據(jù)的功能。另外,SJA1000的RX1引腳與PCA82C250的VREF引腳相連,使用輸入比較器旁路功能,可減少內(nèi)部延時(shí),增加正常通信的總線長(zhǎng)度。

2 軟件系統(tǒng)設(shè)計(jì)

CAN總線節(jié)點(diǎn)的軟件的設(shè)計(jì)主要是對(duì)FPGA進(jìn)行編程,一方面對(duì)飛行模擬器各類接口數(shù)據(jù)的采集和輸出,另一方面是對(duì)SJA1000的接口邏輯程序,來(lái)控制CAN總線的工作方式和工作狀態(tài),進(jìn)行數(shù)據(jù)的發(fā)送和接收。這里主要介紹FPGA對(duì)總線控制器的程序設(shè)計(jì),主要包括對(duì)SJA1000的初始化邏輯、數(shù)據(jù)發(fā)送邏輯和數(shù)據(jù)接收邏輯。由于SJA1000地址總線與數(shù)據(jù)總線復(fù)用,這就需要FPGA不僅要產(chǎn)生SJA1000讀寫控制引腳的信號(hào)邏輯,還需要產(chǎn)生對(duì)SJA1000的尋址信號(hào),實(shí)際上是一個(gè)向SJA1000寫地址的過(guò)程。因此設(shè)計(jì)的關(guān)鍵就是把SJA1000中的寄存器地址當(dāng)成數(shù)據(jù)寫入到SJA1000中,同時(shí)配合地址鎖存信號(hào)ALE和寫允許信號(hào)WR完成對(duì)SJA1000特定寄存器的命令字寫入。

2.1 SJA1000初始化邏輯

初始化邏輯的主要功能是在系統(tǒng)上電或重啟后,對(duì)SJA1000進(jìn)行初始化,以確定工作主頻、波特率、輸出特性等。SJA1000支持兩種模式,即BasicCAN模式和PeliCAN模式,BasicCAN模式是上電后默認(rèn)的操作模式。SJA1000的初始化邏輯主要包括工作方式的設(shè)置、驗(yàn)收濾波方式的設(shè)置、驗(yàn)收屏蔽寄存器(AMR)和驗(yàn)收代碼寄存器(ACH)的設(shè)置、中斷允許寄存器(IER)的設(shè)置、總線定時(shí)寄存器(BTR0、BTR1)、輸出控制寄存器(OCR)和時(shí)鐘分頻器(CDR)的設(shè)置等。在完成SJA1000的初始化設(shè)置以后,SJA1000就可以回到工作狀態(tài),進(jìn)行正常的通信任務(wù)。

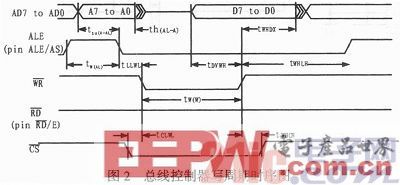

2.2 數(shù)據(jù)發(fā)送邏輯

數(shù)據(jù)發(fā)送邏輯需要FPGA通過(guò)模擬總線的方法對(duì)SJA1000進(jìn)行控制,SJA1000的發(fā)送緩沖區(qū)的寄存器共有11個(gè)字節(jié),其中前3個(gè)字節(jié)分別是幀信息字節(jié)和兩個(gè)標(biāo)識(shí)碼,后8個(gè)字節(jié)是數(shù)據(jù)。發(fā)送時(shí),用戶需要將待發(fā)送的數(shù)據(jù)按特定的格式組合成一幀報(bào)文,送入SJA1000的發(fā)送緩沖區(qū)中,然后啟動(dòng)SJA1000發(fā)送即可。需要注意的是,在向SJA1000發(fā)送緩存區(qū)送報(bào)文之前,必須先判斷發(fā)送緩沖區(qū)是否鎖定,如果鎖定則等待;判斷上次發(fā)送是否完成,如未完成則需等待發(fā)送完成。總線控制器寫周期的時(shí)序圖如圖2所示。

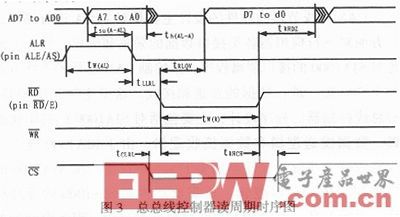

2.3 數(shù)據(jù)接收邏輯

與數(shù)據(jù)發(fā)送邏輯類似,從接收緩沖區(qū)中讀取一條報(bào)文也需要連續(xù)讀取11個(gè)字節(jié),數(shù)據(jù)接收邏輯除了正常的報(bào)文數(shù)據(jù)接收,還要實(shí)現(xiàn)其他情況的處理。對(duì)接收緩沖區(qū)的數(shù)據(jù)讀取完畢后要釋放CAN接收緩沖區(qū)。圖3所示為總線控制器讀周期的時(shí)序圖。

在FPGA程序編寫時(shí),采用狀態(tài)機(jī)完成邏輯的設(shè)計(jì),分別包括初始化狀態(tài)、空閑狀態(tài)、查詢狀態(tài)、數(shù)據(jù)接收狀態(tài)、數(shù)據(jù)發(fā)送狀態(tài)。

3 結(jié)論

在系統(tǒng)設(shè)計(jì)過(guò)程中,采用ALTERA公司的EP1C6型FPGA進(jìn)行設(shè)計(jì),在Quartus II環(huán)境中利用Verilog HDL編程產(chǎn)生SJA1000的片選信號(hào)、地址鎖存信號(hào)以及讀寫信號(hào)等,這些信號(hào)共同驅(qū)動(dòng)SJA1000完成數(shù)據(jù)的發(fā)送和接收。在采用FPGA實(shí)現(xiàn)對(duì)SJA1000的邏輯控制過(guò)程中,采用Quartus II中的SignalTap II Logic Analyzer工具對(duì)FPGA各接口信號(hào)進(jìn)行了測(cè)量,經(jīng)檢查各種邏輯均符合SJA1000的接口時(shí)序要求。

基于FPGA的飛行模擬器通信接口設(shè)計(jì)主要由Verilog語(yǔ)言進(jìn)行描述,易于修改和移植,同時(shí)由于FPGA的I/O豐富,還可以將模擬器中一些常用的開關(guān)量連接到FPGA上,這樣就可以將多種功能集成在一個(gè)FPGA上,相較于采用單片機(jī)控制SJA1000實(shí)現(xiàn)CAN總線通信,本設(shè)計(jì)方案可擴(kuò)展性好,穩(wěn)定性高,能降低成本、系統(tǒng)體積及功耗,在飛行模擬器領(lǐng)域中具有廣泛的應(yīng)用前景。

模擬信號(hào)相關(guān)文章:什么是模擬信號(hào)

fpga相關(guān)文章:fpga是什么

數(shù)字通信相關(guān)文章:數(shù)字通信原理

通信相關(guān)文章:通信原理

分頻器相關(guān)文章:分頻器原理 鎖相環(huán)相關(guān)文章:鎖相環(huán)原理

評(píng)論