G.729A語音編碼TMS320VC5416實(shí)時(shí)實(shí)現(xiàn)

概述

近二十年來,全球半導(dǎo)體產(chǎn)業(yè)的飛速發(fā)展帶動相關(guān)的軟件、硬件設(shè)計(jì)達(dá)到新的水平,使得很多比較復(fù)雜的數(shù)字信號處理算法可以實(shí)時(shí)實(shí)現(xiàn)并且得到廣泛應(yīng)用。突出的代表就是數(shù)字信號處理器(DSP)與語音信號壓縮編碼算法相結(jié)合,并且在日常通信系統(tǒng)中得到廣泛應(yīng)用,例如數(shù)字移動電話、IP電話等。隨著網(wǎng)絡(luò)通信的發(fā)展、微處理器和信號處理專用芯片的發(fā)展,也為語音處理技術(shù)的應(yīng)用提供了更加廣闊的平臺。所有這些因素都促進(jìn)了對更加有效、可靠、高質(zhì)量的語音編碼系統(tǒng)的需要,從而促進(jìn)了語音編碼技術(shù)的持續(xù)發(fā)展。在最近一些年內(nèi),語音壓縮編碼技術(shù)有了很大的發(fā)展。最早的標(biāo)準(zhǔn)化語音編碼標(biāo)準(zhǔn)是70年代CCITT公布的G.711 64kb/s脈沖編碼調(diào)制PCM。此后ITU又先后公布了G.721 32kb/s自適應(yīng)差分編碼(ADPCM)、G.728 16kb/s短延時(shí)碼本激勵(lì)線性預(yù)測編碼(LD-CELP)。此外還有一些政府和組織制定的語音標(biāo)準(zhǔn),例如用于西歐數(shù)字移動通信的13kb/s具有長時(shí)預(yù)測規(guī)則碼激勵(lì)(RPE-LPT)的線性預(yù)測方案,北美數(shù)字移動通信標(biāo)準(zhǔn)8kb/s矢量和激勵(lì)線性預(yù)測(VSELP)方案等。1999年歐洲通信標(biāo)準(zhǔn)協(xié)會(ETSI)推出了基于碼激勵(lì)線性預(yù)測編碼(CELP)的第三代移動通信語音編碼標(biāo)準(zhǔn)自適應(yīng)多速率語音編碼器(AMR),其中最低速率為4.75kb/s,達(dá)到通信質(zhì)量。1995年ITU公布G.723.1,編碼算法有兩種,5.3kb/s的ACELP和6.3kb/s的MP-MLQ算法,主要用于IP電話。1996年ITU公布了G.728 8kb/s的CS-ACELP算法,可以用于IP電話、衛(wèi)星通信、語音存儲等多個(gè)領(lǐng)域。目前,ITU正在致力于制定4kb/s的語音編碼國際標(biāo)準(zhǔn),該算法將達(dá)到長途質(zhì)量。針對一些特殊應(yīng)用,如保密通信、軍用通信、應(yīng)急通信等,許多國際組織、國家也研制了各種不同速率的語音壓縮編碼速率,例如美國政府為保密通信用開發(fā)的2.4和1.2kb/s MELP算法。我國近幾年也研制了0.6、1.2、2.4kb/s及其它速率語音壓縮編碼算法,達(dá)到并且超過了國外同速率編碼的質(zhì)量。

DSP在近20年內(nèi)一直在高速發(fā)展,運(yùn)算能力不斷提高,片上資源和接口更加豐富,而單位運(yùn)算所需功耗不斷降低。下面給出幾個(gè)主要廠家的DSP產(chǎn)品。

TI的DSP主要有四大系列:

C5000系列(定點(diǎn),低功耗):適合

個(gè)人與便攜上網(wǎng)及無線通信應(yīng)用。80-400MIPS。

C2000系列(定點(diǎn),控制器):針對

控制進(jìn)行優(yōu)化的DSP。

C6000系列(高性能):適合寬帶

網(wǎng)絡(luò)和數(shù)字影像應(yīng)用。

OMAP系列(雙核芯片):適合低

功耗移動設(shè)備和多媒體PDA。

ADI的DSP主要有四大系列:

21xx系列:16定點(diǎn)DSP,內(nèi)部REM

大,外圍接口多,適合作為控制類芯片使用。

SHARC系列:32位浮點(diǎn)DSP,21160 21161提供與大內(nèi)存容量結(jié)合的簡單浮點(diǎn)算法,具有高水平的浮點(diǎn)性能。

TigerSHARC系列:比SHARC具

有更高的浮點(diǎn)運(yùn)算功能TS101,TS201

Blackfin系列:高性能16位DSP

信號處理與通用微控制器易使用的性能結(jié)合。

Motolora的DSP:

DSP56800,16BIT定點(diǎn)DSP,通用型DSP。

DSP563XX,24bit定點(diǎn)DSP, 通用型DSP。

本文將介紹使用TI公司C5000系列實(shí)現(xiàn)ITU-T G.729A 8kb/s CS-ACELP語音壓縮編碼算法,并對TI公司的TMS320C54x系列DSPITU-T G.729A語音編碼算法做簡單介紹,以及軟件編程、調(diào)試和實(shí)現(xiàn)結(jié)果。

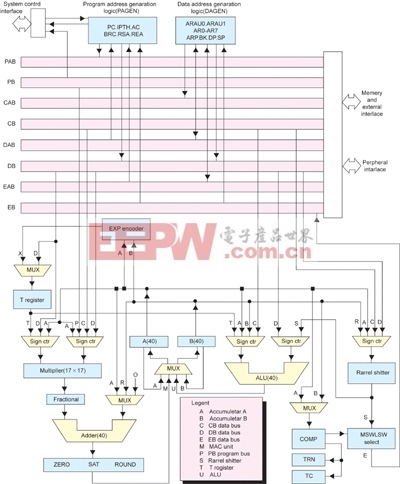

圖1 C54xDSP結(jié)構(gòu)框圖(略)

TMS320 C54x系列DSP芯片簡介及硬件設(shè)計(jì)

TMS320 C54x系列DSP芯片是使用靜態(tài)CMOS技術(shù)制造的。其方框圖見圖1,從圖中可以看出C54x系列DSP芯片具有以下功能單元:

C54x共有八條總線分別是:

PB: 程序讀取總線

CB: 數(shù)據(jù)讀取總線1

DB: 數(shù)據(jù)讀取總線2

EB: 數(shù)據(jù)寫入總線

PAB: 程序讀取地址總線

CAB: 數(shù)據(jù)讀取地址總線1

DAB: 數(shù)據(jù)讀取地址總線2

EAB: 數(shù)據(jù)寫入地址總線

中央處理器(CPU)

CPU由以下幾個(gè)部件組成:

先進(jìn)的多總線結(jié)構(gòu): 包括三個(gè)獨(dú)立的數(shù)據(jù)總線和一個(gè)程序總線

40位的算術(shù)邏輯單元: 包括一個(gè)40位移位器和兩個(gè)獨(dú)立的40位累加器

17bit 17bit的并行乘法器同一個(gè)專用的加法器相配合: 用來執(zhí)行不經(jīng)流水線的單周期乘加(MAC)運(yùn)算

指數(shù)譯碼器: 可以在一個(gè)周期里計(jì)算出一個(gè)40位累加器的指數(shù)值

兩個(gè)地址生成器: 包括8個(gè)輔助寄存器和兩個(gè)輔助寄存器算術(shù)單元

程序控制器: 對指令進(jìn)行解碼、管理流水線和程序流程

片上存儲器

C54x共有192K字的尋址能力(64K字的程序區(qū),64K字的數(shù)據(jù)區(qū),和64K字的I/O區(qū))。

表1給出了部分C54x芯片的片上資源、運(yùn)算能力、工作電壓等。運(yùn)算能力用MIPS來度量,即每秒能執(zhí)行一百萬條指令的數(shù)量。

片上其它資源

C54x系列中不同產(chǎn)品具有不同的片上外設(shè)配置。這些外設(shè)有:

軟件可編程的等待狀態(tài)發(fā)生器

可編程的庫轉(zhuǎn)換

片上鎖相環(huán)時(shí)鐘發(fā)生器(包括一個(gè)內(nèi)部振蕩器或一個(gè)外部時(shí)鐘源)

一個(gè)16比特定時(shí)器

通用輸入輸出管腳

同步串行口

異步串行口

C54x系列DSP芯片具有以下主要特點(diǎn):

采用改進(jìn)哈佛結(jié)構(gòu),對程序內(nèi)存和數(shù)據(jù)內(nèi)存使用分離的總線。這樣可以同時(shí)取指令和操作數(shù),提高了運(yùn)行效率和通用性

先進(jìn)的CPU設(shè)計(jì)和為應(yīng)用設(shè)計(jì)的硬件邏輯提高了芯片的性能

為快速的后續(xù)發(fā)展設(shè)計(jì)的模塊化結(jié)構(gòu)

先進(jìn)的IC處理技術(shù)提供了高性

能和低功耗

采用5V或3V靜態(tài)CMOS技術(shù)

可以進(jìn)一步降低功耗

Power-down模式可以進(jìn)一步降

低功耗

能源消耗控制: 使用IDLE1,IDLE2,和IDLE3指令進(jìn)入Power-down模式

使用CLKOUT-off控制來禁止CLKOUT信號

高度專門的指令結(jié)構(gòu)提供了快速運(yùn)算和優(yōu)化的高階語言操作

單指令循環(huán)和塊指令循環(huán)功能

塊內(nèi)存移動指令提供了更好的程序和數(shù)據(jù)管理

32位操作數(shù)指令

擁有兩個(gè)或三個(gè)操作數(shù)讀取能力的指令

可以并行存儲和并行讀取的算術(shù)指令

條件存儲指令

從中斷快速返回的指令 擁有多種片上外設(shè)和內(nèi)存配置方案

40位算術(shù)運(yùn)算器(ALU)

17bit 17bit單周期并行乘法器

六級流水線操作提高程序執(zhí)行效率

支持比特倒置尋址方式和循環(huán)尋址方式。

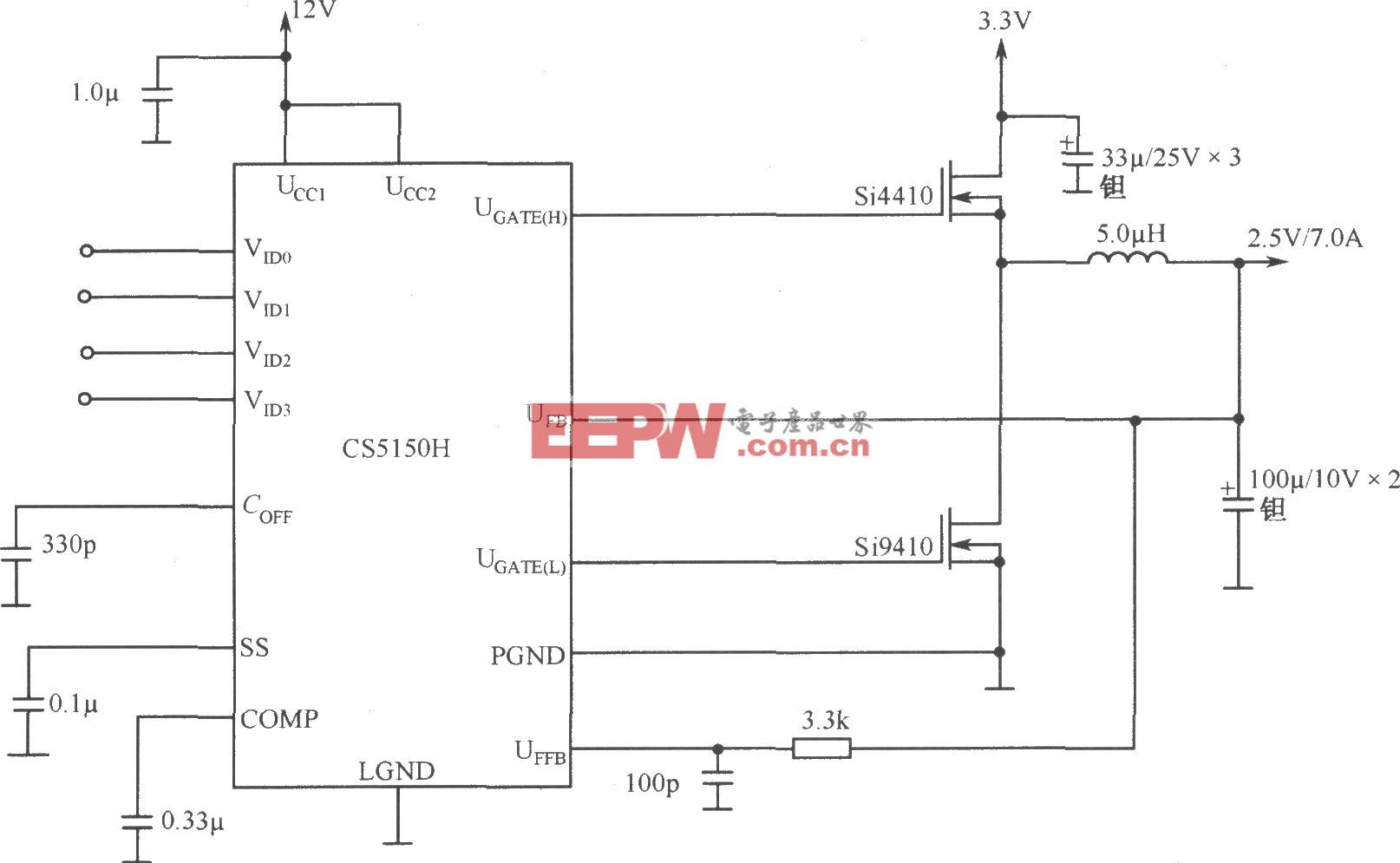

對于語音壓縮編碼,通常所需要的DSP運(yùn)算能力不會超過50個(gè)MIPS,程序和數(shù)據(jù)所占用的容量大約幾十K字,AD/DA的精度保持就可以滿足使用要求,語音輸入輸出、信碼輸入輸出各需要一個(gè)雙向串口。但考慮在通信領(lǐng)域中應(yīng)用,往往一片DSP不僅要實(shí)現(xiàn)語音壓縮編解碼,還需要實(shí)現(xiàn)自適應(yīng)回聲抵消、加解密、信道編解碼,甚至基帶調(diào)制解調(diào)算法等。因此我們選用了TMS320VL5416設(shè)計(jì)硬件平臺。AD/DA芯片采用TI公司的TLV320AIC10,它是德州儀器公司(TI)推出的一款通用型低功耗16位A/D、D/A音頻接口芯片,適用于語音以及寬帶音頻處理。采用3.3V或5V供電,片內(nèi)集成了FIR濾波器,可以達(dá)到最高88KHz的采樣頻率,集成了輸入放大器和輸出放大器,支持多路芯片串連,提供低功耗、ADC與DAC單獨(dú)三種工作模式。TLV320AIC10的數(shù)字接口采用同步串口方式,可以非常方便的與DSP同步串口(McBSP)相連。FLASH采用SST39VF800A芯片,該芯片有512K 16容量,可以將多種應(yīng)用程序固化在該芯片中。開機(jī)后DSP的加載程序自動將FLASH中的程序拷貝到DSP片上RAM中,以便能夠全速運(yùn)行程序,充分發(fā)揮DSP的處理能力。

ITU-T G.729 8kb/s CS—ACELP簡介

國際電信聯(lián)盟(ITU-T)于1995年11月正式通過了G.729。 ITU-T建議G.729也被稱作“共軛結(jié)構(gòu)代數(shù)碼本激勵(lì)線性預(yù)測編碼方案”(CS-ACELP),它是當(dāng)前較新的一種語音壓縮標(biāo)準(zhǔn)。96年ITU-T又制定了G.729的簡化方案G.729A,主要降低了計(jì)算的復(fù)雜度以便于實(shí)時(shí)實(shí)現(xiàn),因此目前使用的都是G.729A。

G.729是由美國、法國、日本和加拿大的幾家著名國際電信實(shí)體聯(lián)合開發(fā)的。它需要符合一些嚴(yán)格的要求,比如在良好的信道條件下要達(dá)到長話質(zhì)量,在有隨機(jī)比特誤碼、發(fā)生幀丟失和多次轉(zhuǎn)接等情況下要有很好的穩(wěn)健性等。這種語音壓縮算法可以應(yīng)用在很廣泛的領(lǐng)域中,包括IP電話、無線通信、數(shù)字衛(wèi)星系統(tǒng)和數(shù)字專用線路。

G.729算法采用“共軛結(jié)構(gòu)代數(shù)碼本激勵(lì)線性預(yù)測編碼方案”(CS-ACELP)算法。這種算法綜合了波形編碼和參數(shù)編碼的優(yōu)點(diǎn),以自適應(yīng)預(yù)測編碼技術(shù)為基礎(chǔ),采用了矢量量化、合成分析和感覺加權(quán)等技術(shù)。

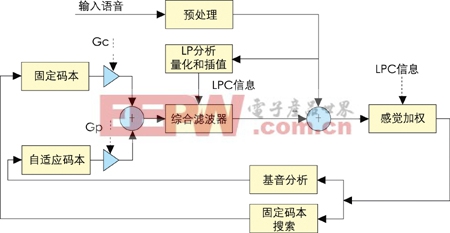

圖1 G.729A編碼器原理圖

編碼器(圖1)對10ms長的語音幀進(jìn)行處理,每幀分為兩個(gè)子幀。輸入語音首先要在預(yù)處理模塊中經(jīng)過高通濾波和幅度壓縮變換,以去除低頻干擾及防止在后面運(yùn)算中出現(xiàn)溢出。每幀進(jìn)行一次線性預(yù)測(LP)分析,并將LPC參數(shù)轉(zhuǎn)換到線譜,對(LSP)形式進(jìn)行預(yù)測式二階段矢量量化(VQ)。然后使用分析合成法,按照合成信號和原始信號間感覺加權(quán)失真最小的準(zhǔn)則來提取激勵(lì)參數(shù)。激勵(lì)參數(shù)(包括固定碼本和自適應(yīng)碼本參數(shù))要每子幀(5ms)計(jì)算一次。每幀要利用感覺加權(quán)語音進(jìn)行一次開環(huán)整數(shù)基值基音延時(shí)估計(jì),然后進(jìn)行閉環(huán)的分?jǐn)?shù)值基音分析,確定自適應(yīng)碼本的延時(shí)和增益,下面再進(jìn)行固定碼本的搜索。固定碼本是使用交織單脈沖排列設(shè)計(jì)的代數(shù)碼本。在搜索時(shí)使用迭代式深度優(yōu)先樹型搜索算法。這種算法的運(yùn)算量比較小,并且具有固定的運(yùn)算復(fù)雜度,比較有利于使用硬件實(shí)現(xiàn)。自適應(yīng)碼本和固定碼本的增益使用預(yù)測式二階段共軛結(jié)構(gòu)碼本進(jìn)行矢量量化。

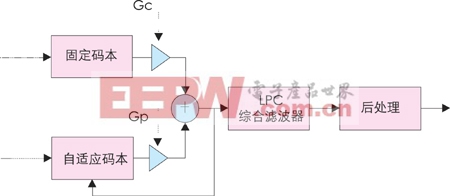

圖2 G.729A解碼器原理圖

圖2給出了解碼算法的框圖。首先要從接收到的碼流中提取LSP系數(shù)和兩個(gè)分?jǐn)?shù)基音延時(shí)、兩個(gè)固定碼本矢量以及兩套自適應(yīng)碼本和固定碼本增益等參數(shù)。然后,對LSP參數(shù)進(jìn)行插值,并轉(zhuǎn)換到線性預(yù)測濾波器系數(shù)的形式。接下來,將自適應(yīng)碼本和固定碼本矢量分別乘以各自的增益再相加,得到激勵(lì)信號。激勵(lì)信號通過LPC綜合濾波器后,就得到了合成語音信號。最后還要對合成語音信號進(jìn)行后處理,以提高合成語音的質(zhì)量。

程序的編制及調(diào)試

程序編制

DSP開發(fā)工具一般都提供C編譯器,可以直接將寫好的C語言程序轉(zhuǎn)換成DSP匯編語言程序,但效率非常低。G.729A算法C語言程序用編譯器轉(zhuǎn)成匯編語言程序運(yùn)行所需要的運(yùn)算量超過2000個(gè)MIPS(每秒百萬條指令),根本無法實(shí)時(shí)運(yùn)行,因此必須手工編寫匯編程序。

由于編解碼的程序規(guī)模很大,又是在DSP的匯編語言級別上實(shí)現(xiàn),因此保持原定點(diǎn)C語言程序所具有的模塊化、結(jié)構(gòu)化的特點(diǎn)對于匯編程序的編寫、檢查、調(diào)試和閱讀都是非常有利的。所以在編程時(shí)盡量保持DSP程序與C語言程序在流程上的一致,具體是使DSP程序與C程序之間保持函數(shù)一一對應(yīng)關(guān)系,保持循環(huán)、分支等結(jié)構(gòu)的一一對應(yīng)。只有為了避免使DSP程序產(chǎn)生過大的不必要開銷時(shí),才對結(jié)構(gòu)進(jìn)行一定的修改,但仍然要保持程序的模塊化和結(jié)構(gòu)化。由于C程序的結(jié)構(gòu)清晰,所以要想作到這一點(diǎn)并不困難,只要為C程序中的if、else、for、while等結(jié)構(gòu)設(shè)計(jì)出相應(yīng)的結(jié)構(gòu)化的DSP匯編程序結(jié)構(gòu),在編程時(shí)按照這種固定對應(yīng)關(guān)系對C語言程序進(jìn)行轉(zhuǎn)換就可以了。

程序的調(diào)試

程序的調(diào)試也是一項(xiàng)很費(fèi)時(shí)的工作。ITU-T針對G.729A提供了8組測試碼,只要通過了這8組測試碼,就可以認(rèn)為程序基本正確了,這8組測試碼分別針對程序中的不同位置而設(shè)定如下:

algthm - 算法中的條件部分

erasure - 幀刪除恢復(fù)

fixed -固定碼本搜索

lsp -LSP系數(shù)量化

overflow -合成器中的溢出檢查

parity -奇偶校驗(yàn)

pitch -基音周期搜索

speech -一般語音文件

tame -訓(xùn)練過程

采用的調(diào)試步驟是首先針對測試碼中最短的algthm.in的第一幀邊編程邊調(diào)試,也就是每編好一個(gè)函數(shù),就將algthm.in的第一幀通過該函數(shù)后的輸出數(shù)據(jù)和C語言的相應(yīng)輸出數(shù)據(jù)相比較,并針對出現(xiàn)的錯(cuò)誤修改函數(shù)內(nèi)容,由于對剛編完的函數(shù)進(jìn)行調(diào)試,對函數(shù)結(jié)構(gòu)和指令記憶會比較清晰。這樣,當(dāng)編碼器完成后,algthm.in的第一幀也就基本通過了。然后再繼續(xù)調(diào)試第二幀,當(dāng)?shù)诙餐ㄟ^后,程序中所剩的錯(cuò)誤也就不多了。等到通過了第10幀,就可以開始大規(guī)模地進(jìn)行仿真了。對于解碼部分,由于程序比較短,就采用了先把全部程序編完,再進(jìn)行調(diào)試的方法。

程序的優(yōu)化

編碼模塊與解碼模塊是按照G.729編解碼器的C語言定點(diǎn)源程序改寫的,雖然定點(diǎn)的C語言程序已經(jīng)為DSP的實(shí)現(xiàn)作了一定的優(yōu)化,但為在一個(gè)DSP芯片上實(shí)現(xiàn)盡量多路的編解碼,必須根據(jù)C54x芯片的功能和特點(diǎn)對程序進(jìn)行一定的優(yōu)化。在編寫DSP程序時(shí),要想提高運(yùn)行效率,就要充分利用C54x DSP芯片具有的各種硬件資源,并適當(dāng)?shù)貙Τ绦蚪Y(jié)構(gòu)進(jìn)行一定調(diào)整,采用的主要方法有以下幾種:

充分利用各種延時(shí)

C54x芯片指令中的跳轉(zhuǎn)、循環(huán)、調(diào)用子函數(shù)等指令都有延時(shí)的格式如B[D],BC[D],RPT[D],RPTB[D],CALL[D],CC[D],RET[D],RC[D]等,這些指令允許利用他們執(zhí)行過程中的等待周期預(yù)先執(zhí)行一兩條其他指令,適當(dāng)調(diào)整程序結(jié)構(gòu)就可以充分利用這些等待周期,從而提高程序執(zhí)行速度。

充分利用塊指令循環(huán)功能

C54x DSP芯片還提供了塊指令循環(huán)功能,此功能可以大大地提高執(zhí)行循環(huán)的速度,但是此功能只能在一重循環(huán)中使用,因?yàn)樗惶峁┝艘粋€(gè)循環(huán)記數(shù)寄存器BRC,所以在遇到多重循環(huán)時(shí)就要盡量把這個(gè)功能用在最里層的循環(huán)中,最里層循環(huán)是執(zhí)行次數(shù)最多的循環(huán)。

利用DSP芯片提供的各種寄存器

適當(dāng)?shù)乩酶鞣N寄存器也能顯著地提高程序的執(zhí)行速度。特別是當(dāng)一個(gè)函數(shù)在程序中被頻繁地調(diào)用,它的賦值可以減少執(zhí)行時(shí)鐘周期。

利用指令中的移位功能

C54x DSP在做賦值和數(shù)值運(yùn)算之前可以自動對操作數(shù)進(jìn)行一定位數(shù)的移位,這樣就可以將移位運(yùn)算和其它運(yùn)算結(jié)合到一條指令中。另外,利用這種移位功能可以代替一些乘數(shù)為2的冪乘法,雖然有這樣的限制,但是在許多濾波器和函數(shù)中確實(shí)有這樣的運(yùn)算,帶立即數(shù)的乘法需要兩個(gè)指令周期,而移位只需一個(gè)指令周期,并且如果條件允許還可以將其結(jié)合到其它指令中,從而大大節(jié)省運(yùn)算量。

利用DELAY指令進(jìn)行賦值操作

另外,在程序中有大量的賦值操作,即將一個(gè)內(nèi)存變量的值賦給另一個(gè)內(nèi)存變量。特別是在搜索碼本的時(shí)候有大量的賦值操作,并且賦值的兩個(gè)變量是固定的。一般的方法是將第一個(gè)變量讀入到累加器或寄存器TREG中,再將累加器的值賦到第二個(gè)變量中。此過程要用兩條單周期指令。C54x提供了一個(gè)移動緩沖區(qū)的指令DELAY,可以在一個(gè)指令周期內(nèi)將內(nèi)存單元的值復(fù)制到它后面的相鄰的內(nèi)存單元內(nèi)。雖然DELAY指令一般是用來移動緩沖區(qū)的,但只要在給變量分配內(nèi)存時(shí)將需要賦值的變量相鄰分配,就可以在一個(gè)指令周期內(nèi)完成賦值操作。

利用寄存器代替某些臨時(shí)變量

程序中往往有很多的臨時(shí)變量,有的臨時(shí)變量應(yīng)用到自始至終,但是有的臨時(shí)變量只是在程序中的某段區(qū)域使用,只是暫時(shí)做數(shù)據(jù)存儲之用,對這類變量就可以酌情使用寄存器代替。由于對寄存器可以直接進(jìn)行操作,而不需要進(jìn)行取數(shù)、存數(shù)操作,從而可以大大提高程序運(yùn)行速度。

盡量利用尋址寄存器

C54x提供了八個(gè)尋址寄存器AR0-AR7,使用它們可以進(jìn)行尋址操作,并且可以控制它們的值隨著指令執(zhí)行而增減。充分利用它們進(jìn)行尋址可以顯著提高運(yùn)行速度。

實(shí)現(xiàn)結(jié)果

運(yùn)算量統(tǒng)計(jì)

在對某一幀實(shí)際語音的處理過程中,編解碼器算法的,各個(gè)部分運(yùn)算量所占比例顯示在表1中。運(yùn)算量較大的部分是LSP系數(shù)的矢量量化與激勵(lì)碼本(自適應(yīng)碼本和隨機(jī)碼本)的搜索。這兩個(gè)部分的運(yùn)算量大約占全部編解碼運(yùn)算量的80%以上。

由于G.729A算法中的LSP系數(shù)的量化、自適應(yīng)碼本和隨機(jī)碼本的搜索等運(yùn)算量較大的部分的計(jì)算復(fù)雜度都是固定的,對于不同的輸入所用的指令周期數(shù)目只有很小的改變,所以整個(gè)編解碼器的運(yùn)算量也是基本固定的,在幀與幀之間只有很小的波動,基本在15MIPS附近波動,其中編碼部分約占13MIPS,解碼部分約占2MIPS。

儲量統(tǒng)計(jì)

G.729a算法所用的存儲量情況見表2。

編碼器和解碼器的存儲量是分別統(tǒng)計(jì)的,它們有很多的共同區(qū)域,如數(shù)據(jù)區(qū)中的表格部分和程序區(qū)的公用函數(shù)部分,所以合并后的數(shù)據(jù)區(qū)和程序區(qū)總存儲量應(yīng)分別為約7K字。

結(jié)束語

本文介紹了采用TI公司TMS320VC5416實(shí)現(xiàn)ITU-T G.729A 8kb/s CS-ACELP語音壓縮編碼,所采用的設(shè)計(jì)思路、程序調(diào)試和程序優(yōu)化的方法對用其它DSP芯片實(shí)現(xiàn)語音壓縮編碼算法也有參考意義。

評論