微機保護控制接口的CPLD抗干擾設計

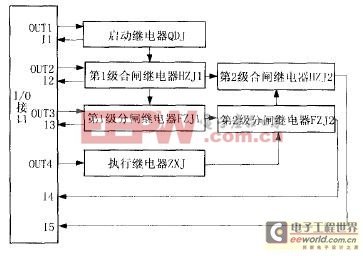

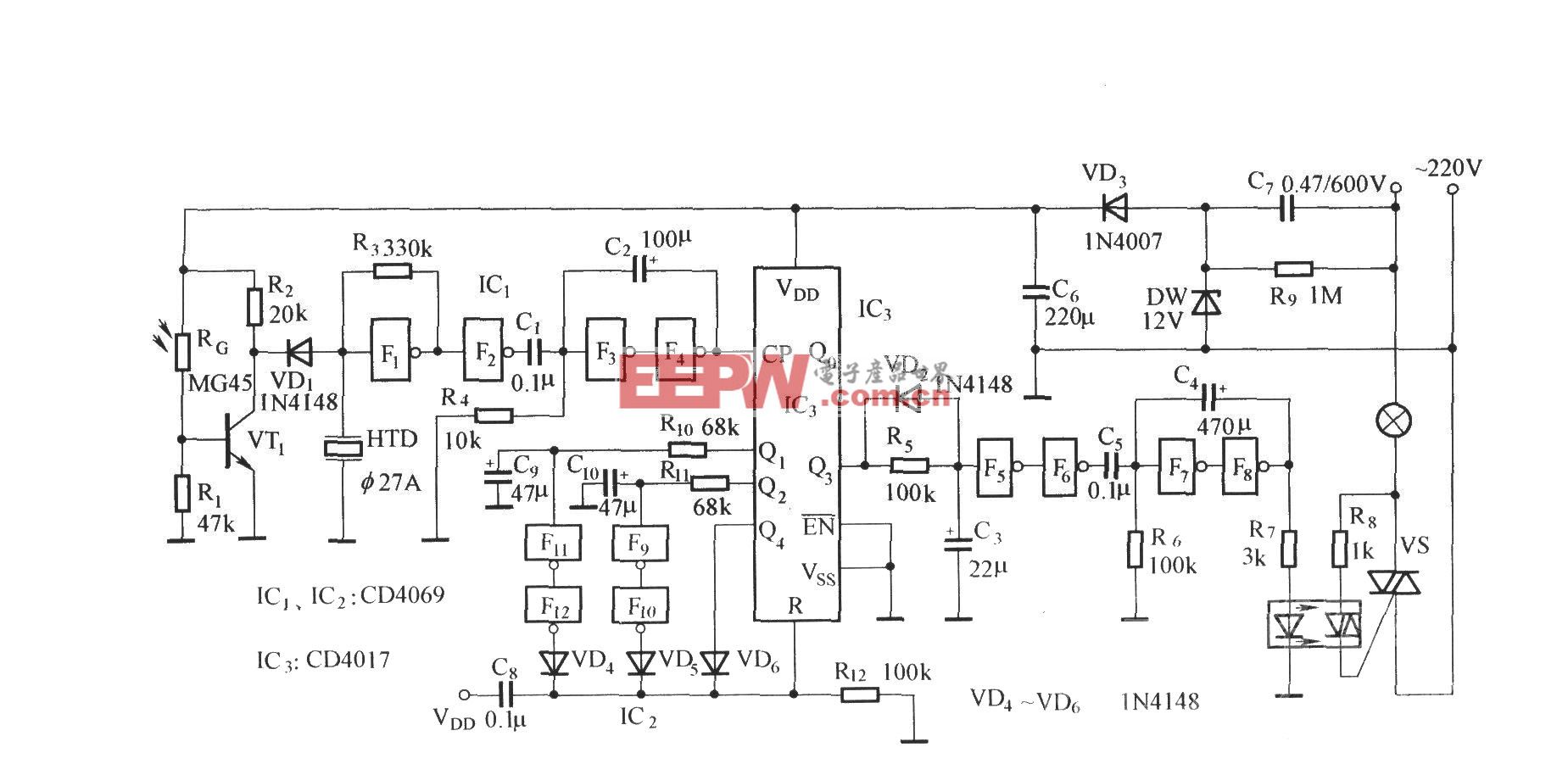

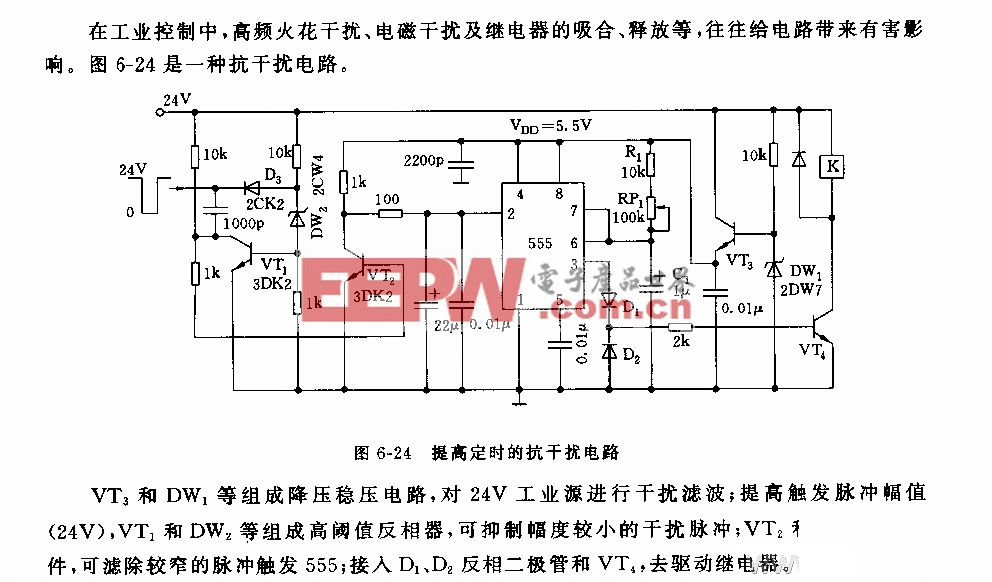

圖1 繼電保護控制出口原理

因此,繼電保護控制出口的閉鎖和冗余度設計是防止控制出口誤動的關鍵所在。嚴格監視分合閘多重命令的執行順序,不允許無序分合閘命令通過,是防止控制出口誤動的根本措施。分合閘多重命令的有序執行,可以看作一個狀態變化序列,用CPLD狀態機對這個狀態序列進行監控,就能杜絕無序狀態的通過,實現控制出口的無干擾控制。

基于CPLD狀態機的抗干擾控制接口設計

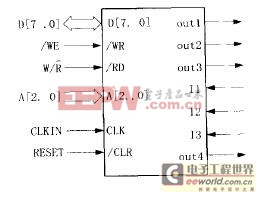

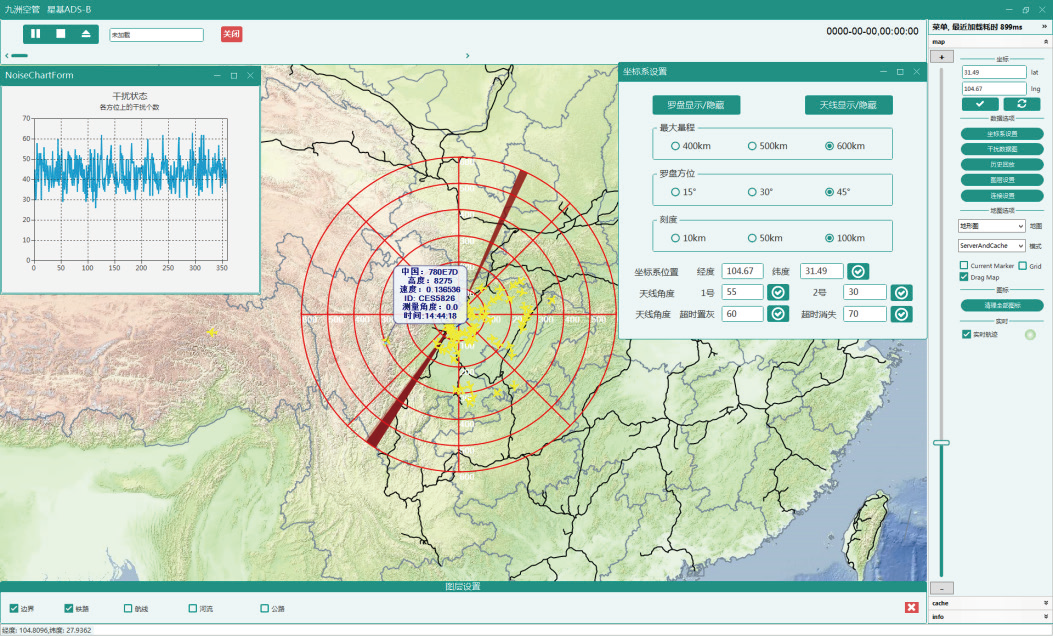

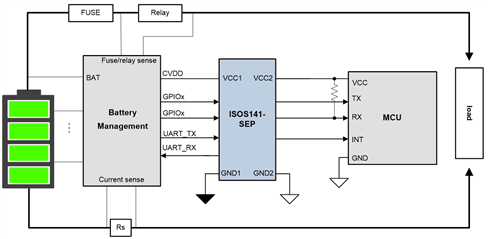

設計一個基于DSP的高壓開關柜微機綜合保護系統時,用一片CPLD芯片實現圖1所示的I/O接口,并設計一個有限狀態機,對狀態輸入I1,I2,I3進行監控,狀態機輸出作為總分合閘命令的允許和禁止信號。基于CPLD的微機保護控制接口如圖2 所示。

圖2 微機保護的CPLD控制接口

分合閘多重命令的狀態編碼

狀態機有3位二進制輸入,共有23=8種狀態。采用二進制編碼方式(Binary coded)將控制接口的初始狀態S0到所有可能的狀態變遷,列成一張編碼表,如表1 所示。狀態編碼表是編寫VHDL程序的基礎。

表1 微機保護控制接口狀態機編碼表

狀態機設計

狀態機的時鐘頻率為5MHz。復位信號/Reset來自DSP微機保護裝置的系統復位信號,對狀態機的狀態初始化。

評論