論NIOS-II系統中A/D數據采集接口的設計與實現

設計方案

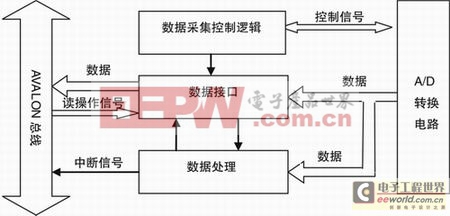

通過對系統需求進行仔細分析,此模塊的功能設計可分為數據采集控制邏輯、數據接口、數據處理邏輯三部分,其整體功能框架圖如圖1。

圖1 模塊功能框圖

說明:AVALON總線主要是用于連接片內處理器與外設,以構成可編程單芯片系統。

功能描述

- 數據采集控制邏輯:產生A/D轉換需要的控制信號。

- 數據接口:提供一個外部A/D采集的數據流向AVALON總線的數據通道,主要是完成速度匹配,接口時序轉換。

- 數據處理單元:此部分主要是提供一些附加功能,如檢測外部信號或內部其它單元的工作狀態,進行簡單信息處理。

設計分析

數據采集控制邏輯

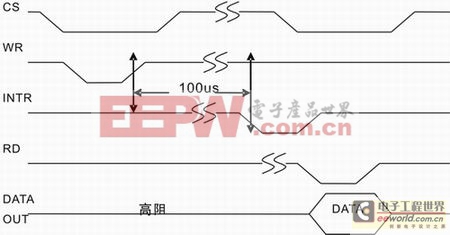

在此以典型的模數轉換芯片ADC0804為例,進行電路設計,ADC0804的數據寬度為8位,數據轉換時間最快為100ms,轉換時鐘信號可以由內部施密特電路和外接RC電路構成的震蕩器產生,也可以直接由外部輸入,其頻率范圍:100KHz~1460KHz。在本設計中ADC0804的時鐘為最大輸入頻率,控制信號時序如圖2。

圖2 ADC0804控制信號時序圖

評論