基于DSP與CPLD的I2C總線接口的設(shè)計與實現(xiàn)

2.3 DSP與CPLD的接口模塊

根據(jù)DSP的時序,DSP與CPLD之間必須根據(jù)雙方(ADSP21992和PCF8583)的時序制定一個握手協(xié)議。當讀程序時,由于I2C總線協(xié)議只能支持最高400kbit/s的傳輸速率,而DSP的同步時鐘可達幾十兆赫。因此,DSP必須等到I2C核把PCF8583的數(shù)據(jù)讀到CPLD后才能獲得正確的數(shù)據(jù)(這里可以通過設(shè)立一個忙標志來實現(xiàn))。而當寫程序時,為了節(jié)約CPLD的資源(數(shù)據(jù)緩存特別占用資源),可以設(shè)置DSP定時輸出數(shù)據(jù)給I2C核,讓I2C核的一次只送一個數(shù)據(jù)。

2.4 硬件設(shè)計

此I2C核可外掛多個帶有I2C總線接口的芯片,可以通過發(fā)送不同的器件地址來選擇。SDA和SCL線必須接上拉電阻。此外,同步時鐘不能太高,否則會影響數(shù)據(jù)傳輸?shù)姆€(wěn)定性。

2.5 時序

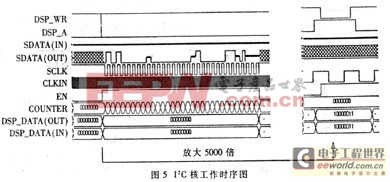

(1)I2C核時序

以寫為例,I2C核時序如圖5所示。

|

(2)PCF8583時序

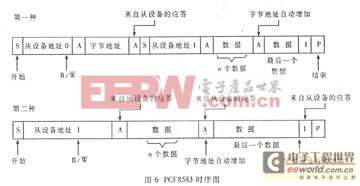

PCF8583的數(shù)據(jù)是8bit一個存儲單元,共256個字節(jié),所以只需要8位地址,而且器件本身有兩種尋址方式:一種是從指定地址開始遞增尋址,另一種是從首地址開始遞增尋址。兩種尋址方式的時序是不一樣的,如圖6所示。

|

3 實現(xiàn)方法

本系統(tǒng)是選用ALTERA公司CPLD7000S系列EPM7128S芯片,并基于MAXPLUSII開發(fā)的。I2C核采用VHDL語言編寫,使用SYNPLIFY 編譯、綜合,用AHDL繪成圖表,用MAXPLUSII仿真和布局。DSP采用VISUAL DSP++2.0編寫。最后分別通過JTAG口下載到芯片并聯(lián)機調(diào)試成功。

隨著DSP芯片和2C通信方式的廣泛應(yīng)用,它們之間的接口問題必須得到解決。本文提出的解決方案具有非常好的可移植性和產(chǎn)品開發(fā)能力。本系統(tǒng)既可以作為一個單獨的系統(tǒng)運行,又可以作為一個通信模塊植入一個大系統(tǒng)中,而其中的I2C核又是一個可移植IP核。利用CPLD的邏輯可編程性,還可以在其剩下的資源中再開發(fā)所需的邏輯器件,既能降低硬件成本又能大大減小系統(tǒng)主板的面積,使電路的設(shè)計更具靈活性。

評論