基于DSP與CPLD的I2C總線接口的設(shè)計(jì)與實(shí)現(xiàn)

PCF8583是一款帶有256字節(jié)靜態(tài)CMOS RAM的時(shí)鐘/日歷芯片。地址和數(shù)據(jù)嚴(yán)格按照雙向雙線制I2C總線協(xié)議傳輸。內(nèi)置地址寄存器在每次讀/寫后自動(dòng)遞增。關(guān)于PCF8583的詳細(xì)說(shuō)明請(qǐng)參看參考文獻(xiàn)。

2.1 系統(tǒng)結(jié)構(gòu)設(shè)計(jì)

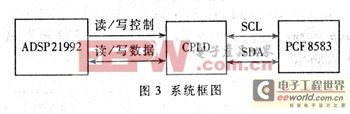

系統(tǒng)的基本功能是通過(guò)CPLD的I2C總線接口完成ADSP21992(主控芯片)與PCF8583的數(shù)據(jù)交換。系統(tǒng)框圖如圖3所示。

|

系統(tǒng)主要由兩個(gè)部分組成:一是DSP與CPLD的接口;另一是I2C核。為了能在DSP指定的時(shí)刻讀/寫PCF8583的數(shù)據(jù),使用DSP的讀寫信號(hào)、同步時(shí)鐘和最高位地址控制數(shù)據(jù)的傳輸。最高位地址作為控制信號(hào)是因?yàn)椋模樱械模桑峡诒容^少,必須優(yōu)先供應(yīng)給其它外設(shè),因此用它來(lái)產(chǎn)生DSP提供給I2C核的片選信號(hào)。而DSP的地址總線位數(shù)較多,最高位一般使用不到,這樣正好可以充分利用資源。

2.2 I2C核

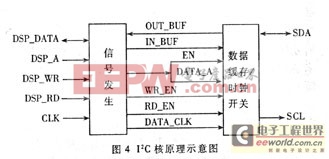

I2C核原理示意圖如圖4所示。

|

整個(gè)I2C核由控制模塊和I/O模塊構(gòu)成。其中,控制模塊包括控制信號(hào)發(fā)生部分和時(shí)鐘開(kāi)關(guān),I/O模塊包括數(shù)據(jù)緩存和同步時(shí)鐘緩存。

當(dāng)DSP的最高地址位出現(xiàn)一個(gè)有效信號(hào)時(shí),便會(huì)使I2C核內(nèi)的觸發(fā)器產(chǎn)生一個(gè)全局使能信號(hào)EN它將會(huì)啟動(dòng)時(shí)鐘、計(jì)數(shù)器和其它控制信號(hào),但數(shù)據(jù)不會(huì)出現(xiàn)交換。如果此時(shí)DSP的讀/寫同步產(chǎn)生,則會(huì)啟動(dòng)相應(yīng)的讀/寫進(jìn)程,進(jìn)行數(shù)據(jù)傳輸。

I2C核的關(guān)鍵技術(shù)是:

①用計(jì)數(shù)器和全局使能信號(hào)EN配合觸發(fā)進(jìn)程。

由于I2C核的片選信號(hào)EN是由觸發(fā)產(chǎn)生的,不能象電平信號(hào)一樣由DSP的I/O控制,因此只能通過(guò)精確的計(jì)數(shù)器定時(shí)和讀/寫使能信號(hào)共同判別控制。

讀/寫使能信號(hào)WR_EN/RD_EN也象EN那樣由觸發(fā)產(chǎn)生,因此也要用同樣的方法判別。

②同步時(shí)鐘的產(chǎn)生。

從圖2中可以看到,數(shù)據(jù)在同步時(shí)鐘的高電平脈沖時(shí)必須保持穩(wěn)定,如果此時(shí)發(fā)生變化將會(huì)被視為一個(gè)控制信號(hào),而通信也會(huì)被中斷。因此,同步時(shí)鐘的高電平脈沖一定要在有效數(shù)據(jù)的中間出現(xiàn)。而所需的控制信號(hào)必須在同步時(shí)鐘正脈沖的時(shí)候出現(xiàn)。

③對(duì)數(shù)據(jù)總線進(jìn)行三態(tài)設(shè)置。 因?yàn)椋樱模梁停模樱校撸模粒裕炼际请p向數(shù)據(jù)線,在寫SDA和DSP_DATA的進(jìn)程中必須設(shè)置高阻態(tài),否則會(huì)出現(xiàn)數(shù)據(jù)線狀態(tài)"不確定"。

評(píng)論