基于ASIC FPGA的IPv6路由器PoS接口設計

4 實現方案

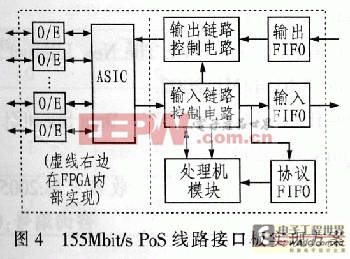

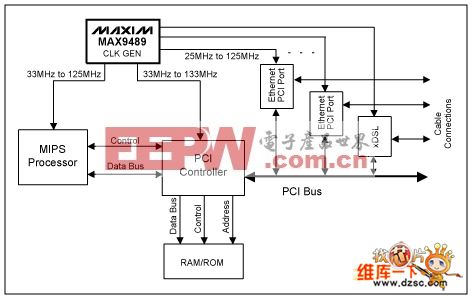

圖4為155Mbit/s PoS接口的實現方案圖。在輸入方向上,從光纖傳入的信號經光電轉換后送入PM5380,完成定時處理、幀同步,從輸入比特流中提取出SDH幀并進而恢復出PPP幀,并按接口緩存于內部8個FIFO中。輸入鏈路處理模塊輪詢讀取PM5380的FIFO,獲得PPP幀并完成PPP相關處理,恢復出IP報文并且完成查IP地址表的工作,將協議報文交處理機,而普通的數據報文合路輸入FIFO,進而通過FPGA的Rocket I/O(高速I/O)送轉發處理。

在輸出方向上,從轉發過來的數據報文 經Rocket I/O送FPGA內部,在輸出鏈路處理模塊中完成與協議報文的合路并且封裝成PPP幀,然后根據內部報文格式中的出接口號來判斷送往ASIC的哪個接口; ASIC完成SDH幀的映射,最后經電光轉換通過光纖送到外部SDH網絡。

5 FPGA設計

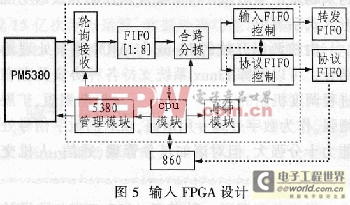

圖5中的虛線框內為輸入FPGA設計原理。輸入FPGA的輪詢接收模塊從PM5380的FIFO中輪詢讀取8個外部接口的數據,并將完整的PPP包緩存;分揀模塊查本地IP表,將協議報文緩存于協議FIFO并經處理機送交主控處理,需轉發的數據報文送轉發FIFO。圖中的MPM5380管理模塊負責產生處理機管理PM5380時所需要的時序,CPU模塊負責和860的交互,時鐘模塊產生系統時鐘,它們是公共模塊。

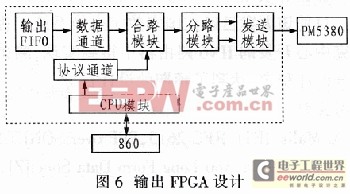

圖6示出輸出FPGA設計原理。從轉發過來的數據經Rocket I/O后緩存于輸出FIFO,合路模塊將數據報文和從處理機下發的協議報文合路送發送模塊按照PM5380要求的時序寫到相應接口的FIFO中發送,但這里必須嚴格滿足PM5380的寫時序要求。

6 結束語

本文根據IPv6路由器155Mbit/s PoS接口的需求,提出并實現了一種基于ASIC+FPGA的設計方案。目前該方案已經在國家數字交換系統工程技術研究中心開發的IPv6路由器中得到實現,測試后的系統性能穩定,達到了預期的設計目標。

評論