基于ASIC FPGA的IPv6路由器PoS接口設計

2 系統設計

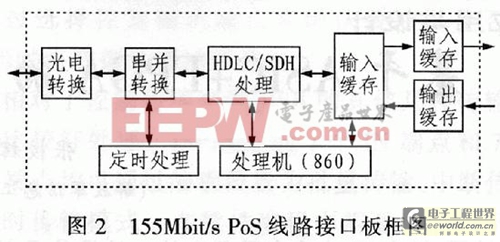

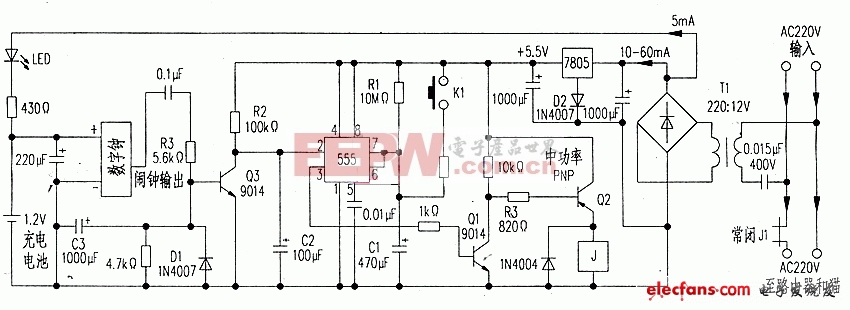

根據155Mbit/s PoS線路接口板要實現的主要功能和PoS的工作原理,可以將155M PoS線路接口分為8個模塊:光電轉換模塊、定時處理模塊、串并轉換模塊、SDH和HDLC處理模塊、PPP處理模塊、處理機模塊、輸入緩存模塊和輸出緩存模塊,其邏輯結構框圖如圖2所示。

其中,光電轉換模塊主要實現光信號和電信號之間的轉換。定時處理模塊負責從接收的串行數據中提取時鐘信號。串并轉換模塊實現串行數據和并行數據之間的轉換。在接收方向上,在對信號進行串并轉換之前,對于串行的輸入數據需要進行幀和字節邊界的檢測。SDH和HDLC處理模塊是155M PoS線路接口的關鍵模塊,完成STM-1的映身教處理及HDLC幀格式的封裝和拆裝。PPP處理模塊主要完成對PPP分組的硬件處理。處理機模塊負責單板的初始化、狀態監測和控制、處理PPP協議分組以及與主控通信等任務。輸入緩存用來存放線路接口發送轉發處理的數據包,輸出緩存用來存放調度輸出后送給線路接口的數據包。

根據目前的技術水平,可選擇如下方案:光電轉換模塊由專用的光電器件完成,串并轉換、定時處理、HDLC/SDH等物理層處理功能由專用電路完成,而PPP處理由FPGA完成。

3 關鍵電路的選型及說明

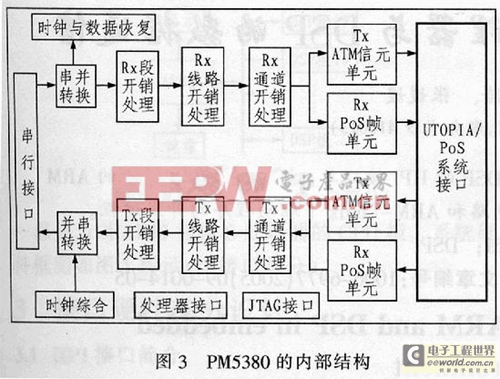

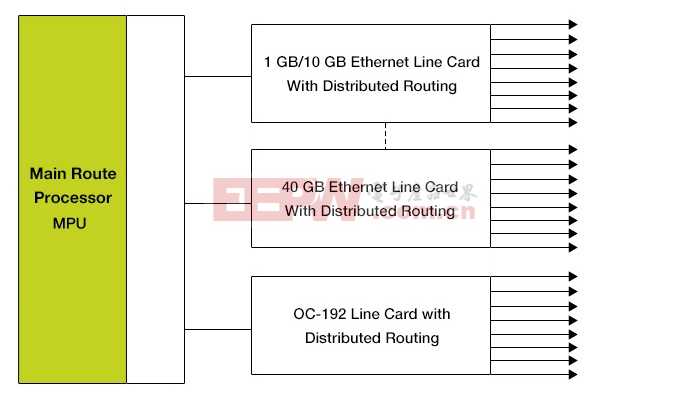

物理層處理電路采用PMC公司的PM5380,它是一款新型的PoS/ATM專用處理電路,支持8路獨立的ATM/PoS接口。該電路具有極高的集成度,將定時提取模塊、串行轉換模塊、段開銷處理模塊、通道開銷處理模塊、路開銷處理模塊和HDLC處理模塊等集成到一起,功能非常強大。其內部結構見圖3。

PM5380的設計符合IETF PPP工作組提出的PPP over SDH/SONET規范;支持8路全雙工155Mbit/s的STM-1接口,并帶有數據和時鐘恢復(CDR)電路;完全符合Utopia-2接口規范, 支持多地址和奇偶校驗;對PoS應用提供相當于Utopia-2的系統接口,16位總線寬度,支持包傳送和字節傳送,內置8個FIFO緩存對應接口的數據;提供串行的155Mbit/s的接口與光器件對接,并且都是差分線路;提供一個通用的八位微處理器接口來完成PM5380的初始化配置、工作控制以及狀態監測;支持線路環回、串行環回和并行環回;單電源3.3VCMOS制作工藝,輸入兼容PECL和TTL電平,輸出為TTL電平。在本設計中,需要通過處理機配置相應的寄存器,使PM5380工作于PoS模式。

FPGA選用Xilinx公司VIRTEX-II PRO,該電路是300萬門級的FPGA,其高速I/O模塊可提供多達16路Rocket I/O,內置Power PC核提供高性能的數字時鐘管理,并且具有強大的開發軟件支持。

評論