基于SDI接口的實時圖像增強顯示系統

經黑白相機輸入的圖像數據經過協議轉換處理后得到的是SDI接口視頻YCbCr格式中亮度Y分量,這時將CbCr在程序里填充80h,就構成YebCr信號,而后用于輸出顯示,為了增強顯示效果,顏色更加能豐富人眼的視覺效果,下面給出一個算法將灰度轉換為偽彩色。

實現偽彩處理,通常是把當前像素灰度值作為存儲地址查找RGB偽彩碼表,將碼表中對應的RGB三色值用RGB轉換到YebCr彩色區間,而后輸出偽彩圖像。在FPGA里實現的基本方法是最大限度地利用FPGA的IP核,將RGB碼表寫到FPGA的內嵌RAM核里,在程序中依次遍歷查找表和計算下面的公式計算出相應的CbCr值并且輸出。

R=1.164(Y-16)+1.596(Cr-128)

G=1.164(Y-16)-0.813(Cr-128)-0.391(Cb-128)

B=1.164(Y-16)+2.018(Cb-128)

2.3 畫幅縮放

圖像的畫幅縮放也被稱為圖像重采樣,它是視頻處理中的一項重要技術。在SDI顯示輸出模塊中,由于標清SDI顯示畫幅分辨率是720× 576,前端輸入CameraLink或者其他接口的圖像分辨率隨機,所以必然會用到圖像畫幅縮放,否則,如果圖像分辨率超出SDI的這個范圍,就會導致顯示不全,如果分辨率小于這個范圍,就會導致有黑框,直接影響后續的顯示效果。

目前畫幅縮放的算法種類繁多,但基本方法都是插值運算方面的算法,例如最近鄰插值、雙線性插值以及立方卷積插值算法等,但最近鄰插值算法在亮度變化比較快的圖像邊緣比較粗糙;立方卷積插值算法非常復雜而且運算量大,不滿足實時處理條件。同前面2種插值算法比較,雙線性插值算法運算量少、實時性高,適合于在FPGA內部實現。

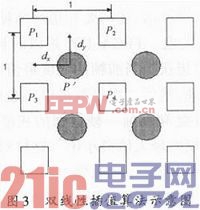

如圖3所示,假設原始圖像中的某點(x,y),則相鄰的右側和下方像素點位置為(x+1,y),(x,y+1),(x+1,y+1),假設它們的灰度值分別是P1,P2,P3,P4,在水平方向和垂直方向上的位移都是單位1,并假設待插入點的位置坐標為:(x+dx,y+dy)。

那么根據雙線性插值算法原理得到插入點的灰度值為:

P’(x+dx,y+dy)=(1-dx)(1-dy)P1+dx(1-dy)P2+dy(1-dx)P3+dxdyP4

化簡后得到:

P’(x+dx,y+dy)=P1+(P2-P1)dx+(P3-P1)dy+[(P4-P3)-(P2-P1)]dxdy

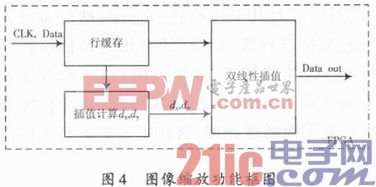

從上式看出,當知道待插值點的偏移距離dx和dy后,那么該插值像素點的灰度值可根據周圍的4點得到。該系統中的畫幅縮放處理正是采用雙線性插值算法,其在FPGA內部實現的具體功能如框圖4所示,主要由數據緩存單元、雙線性插值單元、插值系數控制單元組成。

在實現圖像縮放算法以前,首要算出圖像的縮放因子k。這里以一行圖像為例,以單位長度“1”表示相鄰2個像素的距離,圖像縮放前的分辨率為A×1,圖像縮放后的分辨率為B×1,則縮放前后的圖像的像素縮放因子k=B/A。例如,分辨率為640x512的圖像縮放為720x576的圖像,則在水平方向上縮放因子k=1.25;垂直方向上的縮放因子k=1.125;根據不同的情況,在水平、垂直方向上的縮放比例因子不同。

根據圖4和插值的運算公式,每經過一個像素時鐘,插值系數dx,dy需要實時提供給插值運算模塊,這就要求FPGA時序同步,并且FPGA各個功能模塊能夠有效配合。

3 實驗結果及分析

將硬件系統和相機連接,該相機基本參數是320x256分辨率,14 b像素深度,幀頻25/50可調。通過PC機的RS 232串口連接轉一個轉換設備,使之滿足RS 422差分協議,以便發送命令給硬件系統和返回硬件系統狀態。

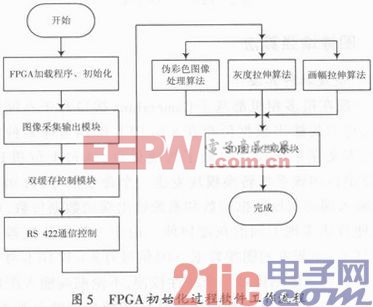

FPGA程序采用模塊化方式,分為圖像采集輸出模塊、雙緩存控制模塊、通信控制模塊、偽彩處理模塊、灰度拉伸模塊、畫幅縮放模塊和SDI時序生成模塊,其中偽彩處理模塊、灰度拉伸模塊和畫幅縮放模塊通過RS 422接口發送不同的指令給FPGA,就會觸發相應的模塊工作,具體FPGA初始化過程中軟件工作流程如圖5所示。

評論