Alpha MOS在PFC應用中的注意事項與設計要點

3 Alpha MOS的并聯及PCB設計

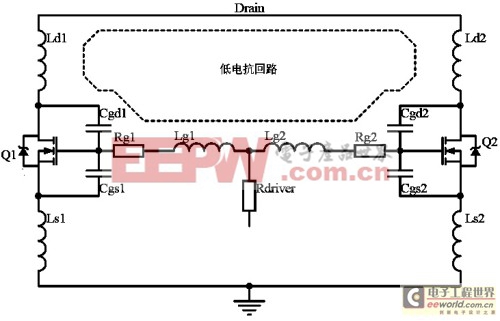

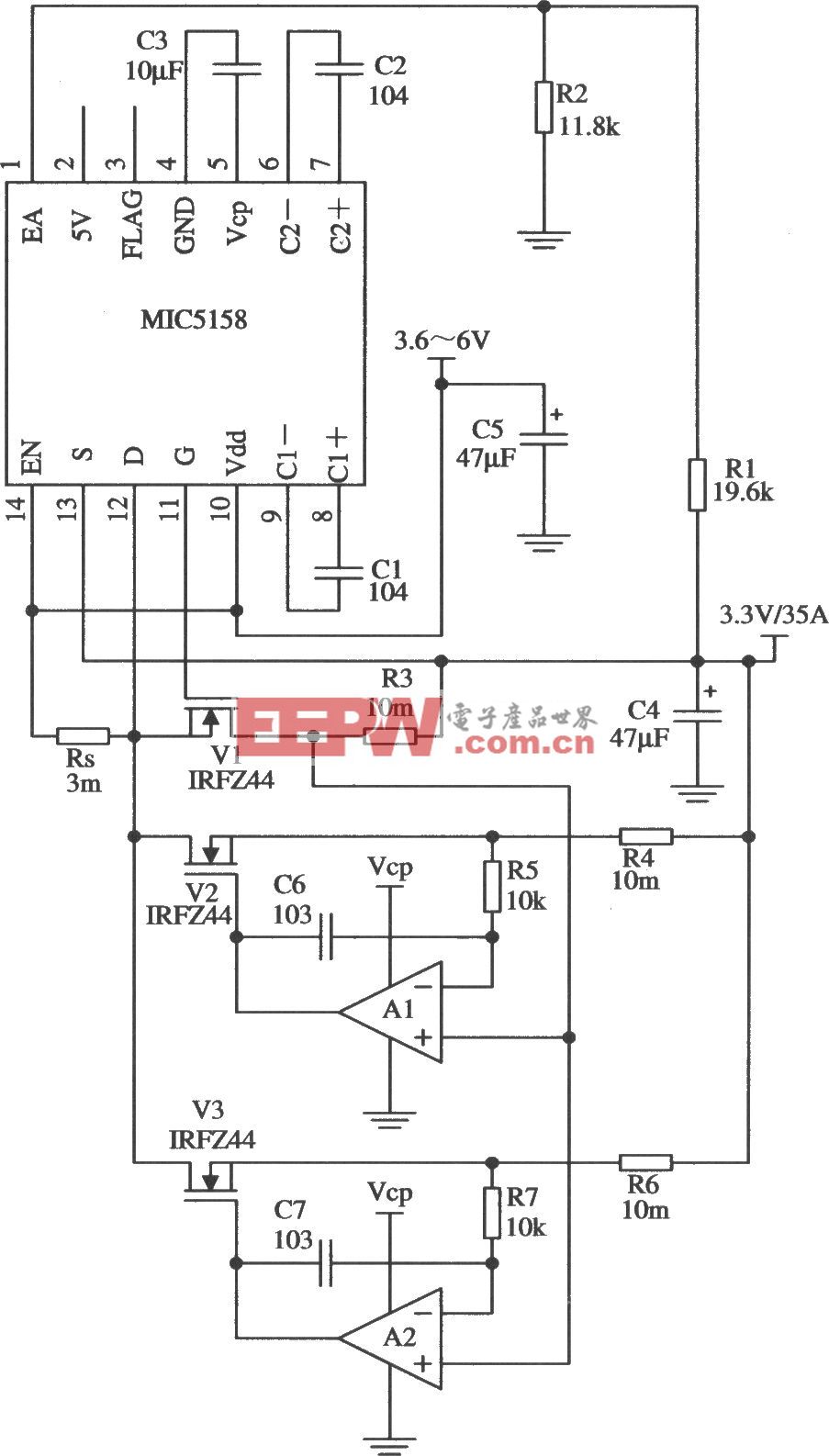

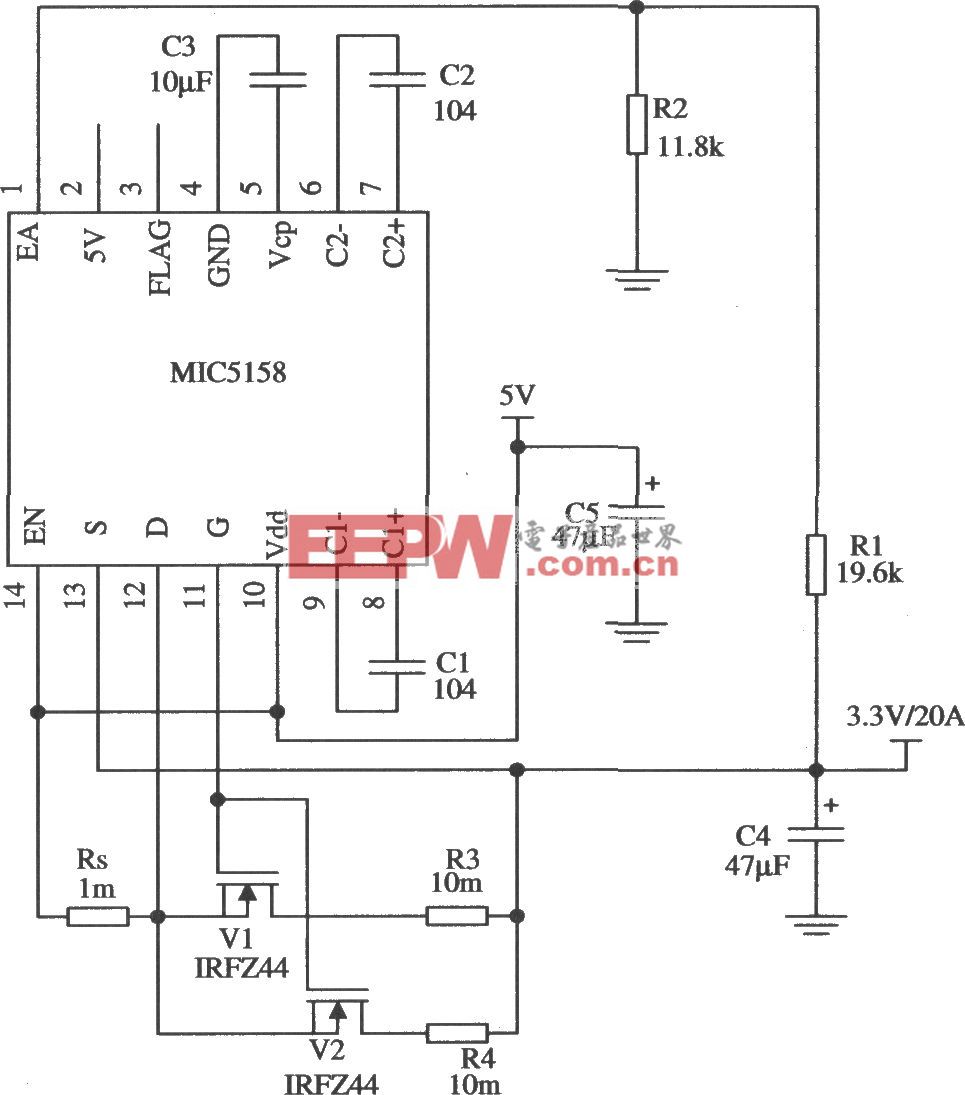

對于MOS并聯的情況,首先驅動電路要盡可能隔離。嚴禁直接將并聯MOS的驅動端連在一起。由于MOS的漏極電感,結電容以及門檻電壓等可能有差異,直接將門極相連會使門極驅動在開關過程產生振蕩,如圖13所示,振蕩將在低電抗回路中發生,嚴重時會導致MOS損壞。驅動電阻增大可以對并聯振蕩起到衰減作用,最好嚴格地隔離并聯驅動。

圖13:直接并聯的驅動干擾模型

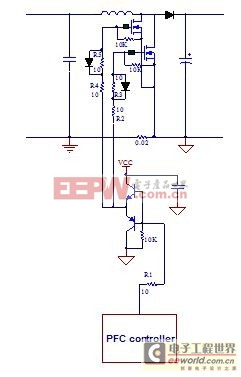

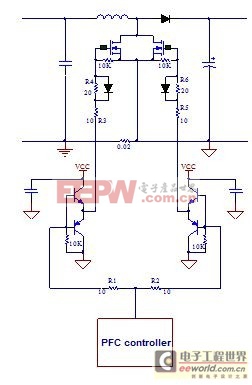

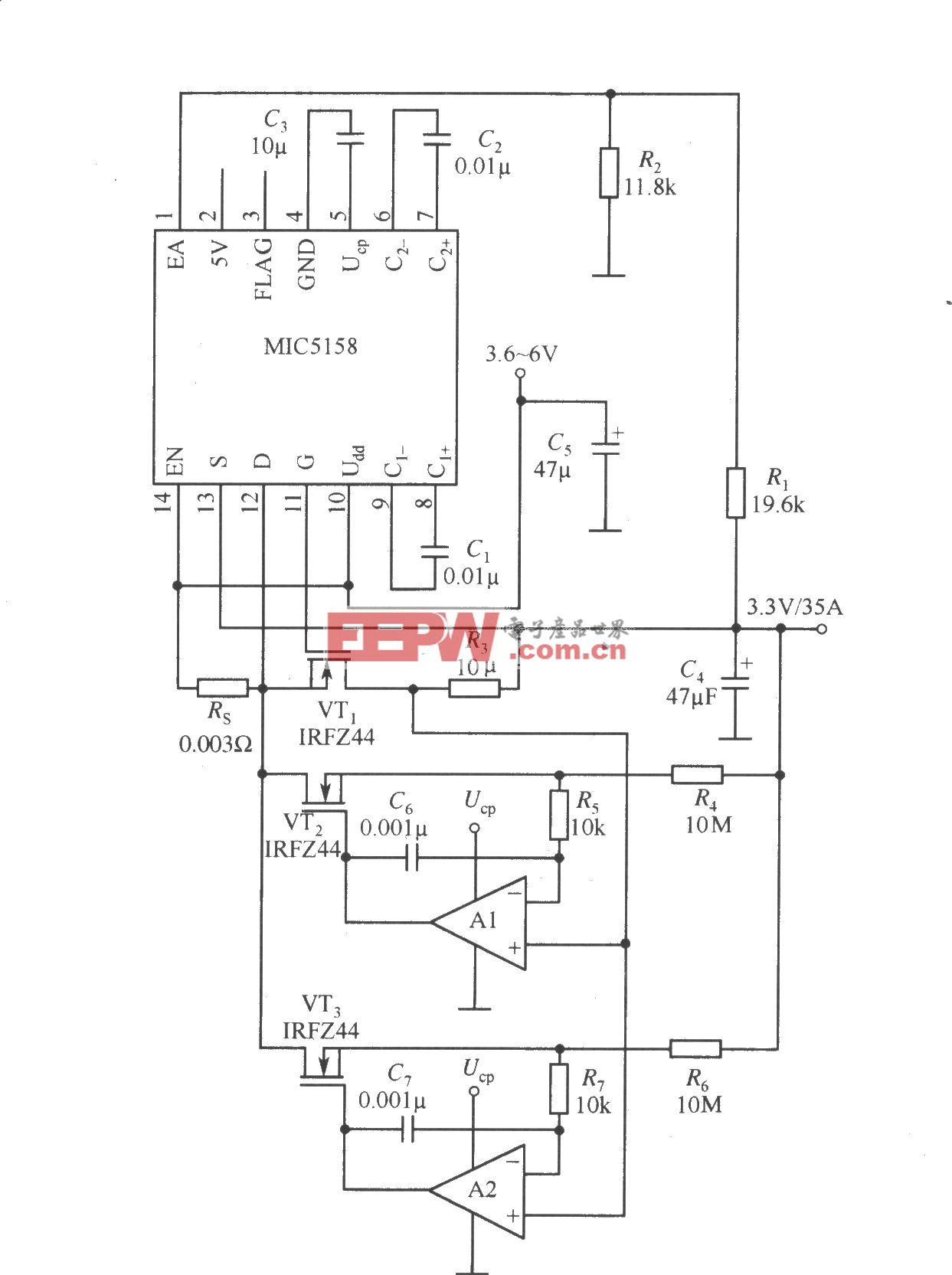

圖14所示為常見的并聯方式,并聯的MOS分別通過驅動電阻與圖騰柱電路相連。但這種隔離還不夠徹底,徹底隔離的方式如圖15電路所示,兩個MOS分別經過各自獨立的驅動電路驅動,只在信號輸出端相連。不管采用哪種驅動方式,為了提高可靠性,增大驅動電阻,降低dv/dt(比單管更低)都是必要的。

需要說明的是,在并聯應用中,驅動受干擾的問題要優先于并聯的不平衡問題。一般的電路中很難保證并聯的絕對平衡。如果驅動電路和PCB布局不能兼顧的情況下,可以適當犧牲一些平衡性,但驅動的干擾必須被消除。具體應用中需要仔細權衡。

圖14:常用并聯驅動電路

圖15:完全隔離并聯驅動電路

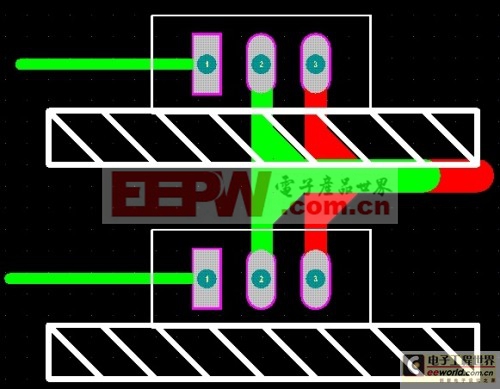

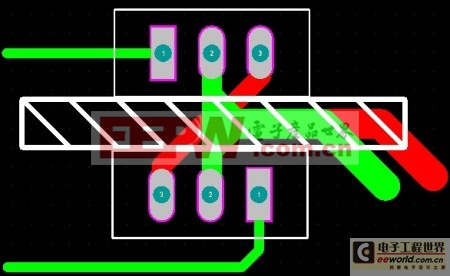

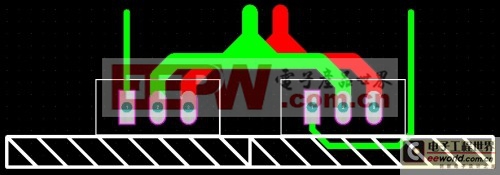

并聯中PCB布局和走線十分重要,越是高速開關的MOS,對并聯均衡的要求就越高。不均衡的并聯,不但會導致單個MOS承受過高的電流沖擊和dv/dt(注意到dv/dt與電流成正比)還會在電流重分配的過程中產生振蕩,干擾驅動和其他信號。下面是一些MOSFET并聯的例子,綠色為正面走線,紅色為背面走線。

圖16和圖17是最佳的并聯走線方式,并聯的MOS各自漏極和源級的走線長度相同,驅動走線與主功率走線在不同方向。實際應用中可以增大走線面積以取得更好的效果。

圖16:并聯MOS散熱片獨立

圖17:并聯MOS散熱片共用(背靠背)

圖18的MOS布局方式在一些中小功率應用中比較常見,采用這種走線方式可以取得均衡的效果,但是實際應用要注意減少走線長度以減小走線電感。

圖18:并聯MOS散熱片共用(并排)

圖19是一種不良走線方式,左邊的MOS上串聯了一段走線電阻和電感,這可能導致右邊MOS的工作電流更大,dv/dt和di/dt也更大

圖19:并聯MOS散熱片共用(并排),不良走線

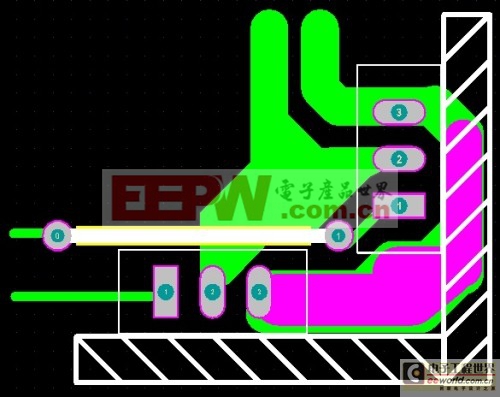

在一些中小功率的實際應用中,PCB是單面板,常常采用圖20的方式并聯。雖然這種方式仍然不能實現走線電感的均衡,但是通過走線露銅涂錫,減少了電阻的不平衡。

圖20:并聯MOS散熱片共用(并排),單面板小功率

圖16和圖17的布局方式不是很容易實現,圖21是單面板PCB,并聯MOS在散熱片拐角處放置,通過增加走線面積和露銅等方式,可以在一定程度上減少不均衡問題。

圖21:并聯MOS散熱片直角布局,單面板

總結

Alpha MOS是AOS新一代高壓MOSFET產品,它具有導通電阻小,開關速度快,結電容小的特點。Alpha MOS在PFC的應用需要特別謹慎,盡量通過增大Rg,增加Cgs等方法控制dv/dt小于20V/ns,并控制啟動過程抑制沖擊電流。由于Alpha MOS的高速開關特性,需要注意驅動電路設計和PCB版布局,盡量減少干擾,在并聯應用中也需要采用獨立的驅動電路和合理的PCB走線。

評論