鋰離子電池管理芯片的研究及其低功耗設計 — 數模混合電路的低功

③編碼優化

常用的二進制編碼中,采用所有空閑的高位作符號擴展位,這將增加耗能的跳變。符號-數值編碼(如格雷碼等)方法只用最高位代表符號,如果用它來代替二進制編碼,可以減少由于數據符號改變而產生的功耗。

2)動態功耗管理技術

是系統級功耗優化中的一個有效手段。根據負載的請求,子系統可以分為工作和空閑模式。在空閑模式下,可以將子系統關斷,進入低功耗的待機(Standby)

和不消耗能量的睡眠(Sleep)狀態;反之,則將子系統喚醒,進入正常的工作模式。

這種有選擇地關斷空閑的子系統,降低功耗的效果十分顯著,如在PC系統級功耗管理中,最常見的是將無執行任務的硬盤和顯示器關斷以節省功耗。

這種方案的局限性在于,在功耗狀態切換過程中,通常有延遲,喚醒處于睡眠狀態的子系統也需要更多的能量。因此,DPM技術需要解決以下問題:一是何時將子系統關斷,關斷多久;二是是否值得關斷,即恢復狀態是否需要更多的能量。這些都是判決策略需要研究的內容,目前最常用的方法可分為三種:基于超時(Timeout)的方法、基于預估算(Predictive)的方法、基于隨機理論(Stochastic)的方法。

和上述改變子系統的功耗狀態不同,動態電壓等比例變化(Dynamic Voltage Scaling, DVS)技術是根據系統的工作狀態,基于區間(Interval-based)或基于線程(Thread-based)來預測系統負載[33,34],動態地改變系統的工作電壓。動態電壓和頻率等比例變化(Dynamic Voltage and Frequency Scaling)技術則是同時改變工作電壓和頻率,獲得最低的系統功耗。

和靜態低功耗設計相比,DPM技術由于要預測系統和負載、系統和電源的關系,動態地調整工作狀態、電壓和頻率,對系統工作狀態的建模、預測算法都更復雜,有更多的工作急待開展,但是可以肯定的是,DPM技術降低功耗的效果也更顯著。

2寄存器傳輸級

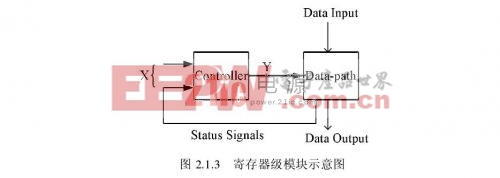

作為綜合(排序和分配)的高層次結構,RTL層次將包含一個控制部分(也稱控制器)和一個操作部分(也稱數據通路),如圖2.1. 3所示。

數據通路以寄存器為特征,而控制器是由組合邏輯來實現,因此,RTL級低功耗設計的對象將是時序和組合邏輯,這可以采用硬件描述語言VHDL和VERILOG來實現。另外,RTL的抽象層次決定了它不可能涉及電源電壓和電容,因此降低功耗的途徑主要是降低開關活動因子,即減小寄存器和組合邏輯的跳變頻率。

1)操作數

在RTL層次,操作數分離(Operand Isolation )是針對組合邏輯最常用的低功耗技術,其本質是在組合邏輯模塊間加入一個鎖存器,當鎖存器的使能無效時,寄存器保存值不加以更新,組合路徑被隔斷[36,37]。只有在進行有效運算時,組合邏輯才有耗能的跳變產生,這樣便降低了此模塊的功耗。

操作數變形(Operand Transformation)有時也稱為數據通路的重排序,即是指在不影響邏輯功能的條件下,以翻轉頻率最低為策略,對電路單元重新排序來降低功耗的技術。

評論