鋰離子電池管理芯片的研究及其低功耗設計 — 數模混合電路的低功

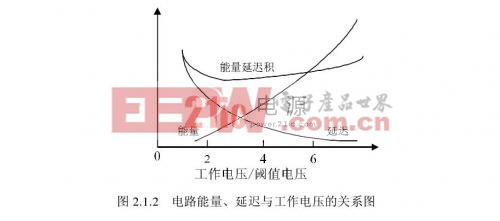

第四,降低工作的電源電壓V DD。由于功耗和電源電壓的平方項成正比,所以這也是降低功耗最有效的方法。但在工藝尺寸確定、一級近似條件下,電路延遲與VDD滿足下式

即有Td∝(CdVDD)/(VDD-VTH)2,其中W和L分別是器件的柵寬和柵長,μ為載流子遷移率,COX為氧化層電容,VTH為MOS管閾值電壓。

正如圖2.1.2所示,從電路能量、延遲和工作電壓的關系中可以看出,當VDD在2.5VTH到6VTH的范圍內,延遲和能量延遲積的變化比較平緩,在VDD=3VTH時,這兩者達到最低值。當工作電壓繼續下降到接近VTH時,延遲將急劇上升。

為了改善VDD下降引起的電路速度下降,可以采用并行或流水線結構,但這將使電路面積增大;另外一種補償方法是,通過降低V TH來增大VDD /VTH值,但同時電路漏泄電流將增加,這時可以采用可變電壓、可變閾值電壓技術解決;在一些非關鍵電路中,也可以采用多電壓、多閾值電壓技術加以補償。

2.1.2數字電路的低功耗設計方法

在目前ASIC設計過程中,常采用的是自頂向下(Top-Down)流程。對功耗的優化也就可以考慮到,在不同的設計層次,有目的地選擇上述影響功耗的因素,在給定的性能約束下,實現功耗最小化的目標。

從抽象層次來分,低功耗設計可以分為:系統級、結構級/算法級、寄存器傳輸級、邏輯/門級和版圖級。在設計的不同層次,影響功耗的因素所起的作用各不相同,因此功耗優化的效果也不同;綜合地看,在芯片設計時越早考慮低功耗,取得的效果也越顯著。

1系統、結構級

在這個層次上,從系統功能出發,分為靜態低功耗設計和動態功耗管理(Dynamic Power Management,DPM)技術兩種。靜態低功耗設計是在考慮系統的具體實現時,采用不同的電路結構和不同的編碼方式,在設計階段(如綜合和編輯)實現低功耗;而動態功耗管理技術是和運行期間的行為密切相關,它需要充分考慮系統和任務或者和負載的關系,做出相應的判決,來實現低功耗。

1)靜態低功耗方法

①電路結構

并行(Parallelism)結構是將一個數據處理功能模塊分為幾個相同的子模塊,并行處理數據,然后選擇對應的輸出。這種方案允許在保持總模塊速度不變的情況下,降低各個子模塊的電壓、頻率等因素,使總功耗降低,但代價是將增加芯片的面積。

流水線(Pipeline)結構是在保持總體速度不變的前提下,將數據分段后連續慢速處理,速度余量則可以通過降低電壓來降低功耗。如果和并行結構相結合,就可以取得更好的功耗節省效果。

②電壓技術

和改進電路結構一樣,電壓技術也是為了

評論