鋰離子電池管理芯片的研究及其低功耗設計 — 數(shù)模混合電路的低功

2.1數(shù)字電路的低功耗設計

2.1.1數(shù)字電路的功耗模型和影響因素

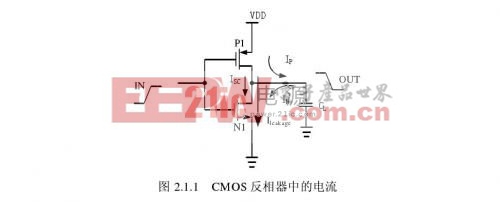

以圖2.1.1所示的最基本的反相器單元為例,CMOS數(shù)字電路的功耗可以分為靜態(tài)功耗和動態(tài)功耗兩個部分:

其中,靜態(tài)功耗

式中,第一項是P1和N1同時導通時的直流短路電流I SC引起的靜態(tài)功耗;第二項是由漏泄電流引起,包括亞閾值電流和源漏區(qū)與襯底反向偏置時的漏泄電流。

動態(tài)功耗是對電路節(jié)點等效負載電容進行充放電所消耗的,也稱為開關功耗,可表示為

式中,α0→1是開關活動因子,表示每個時鐘周期內的狀態(tài)跳變次數(shù),其大小與電路結構、邏輯功能、輸入信號的狀態(tài)和節(jié)點的初始狀態(tài)有關,一般地,CMOS電路中有α0→1≤1;CL是等效負載電容;?是時鐘頻率;VDD是電源電壓。

在0.18μm及其以上的CMOS電路功耗中,占主導地位的是動態(tài)功耗,有時還需要考慮短路功耗,而在一般情況下,漏泄電流和穩(wěn)態(tài)偏置電流功耗都可以忽略。因此,要降低電路功耗,必然要從降低動態(tài)功耗入手,可以說,式(2.1.3)是低功耗數(shù)字電路的指導公式。

式(2.1.3)可以看出,降低電路的動態(tài)功耗,可以有以下四種途徑:

第一,降低開關活動因子α0→1。在每個時鐘周期內,并不是所有節(jié)點的狀態(tài)都發(fā)生跳變,也不是所有狀態(tài)的跳變都要消耗能量(如1→0的狀態(tài)轉變),所以降低開關活動因子的本質是,根據(jù)輸入信號的組合狀況,通過優(yōu)化算法、邏輯結構等方法,減小不必要的耗能跳變。常采用的方法有,門控時鐘技術、功耗估算/優(yōu)化CAD技術和降低跳變編碼技術。由于快速、準確地估算α0→1有很大的難度,所以急待開發(fā)實用的功耗估算CAD技術;其次,降低α0→1來降低動態(tài)功耗十分有效,并且有很大的潛力,所以這也是低功耗研究的重要方面之一。

第二,降低等效負載電容CL。CL主要由兩方面構成:一方面是后續(xù)門的輸入門電容和反相器源漏區(qū)的電容,它們和器件工藝有關;另一方面互連線電容。

因此要降低CL,可以采用優(yōu)化邏輯電路(如減小所用晶體管數(shù)目)、優(yōu)化晶體管尺寸、工藝映射中降低高活動因子的電容、版圖中合理布局等方法。可以說,在設計的各個層次,都需要考慮到CL對功耗的影響。

第三,降低工作頻率f.如果僅僅通過降低電路的頻率來降低功耗,則它必然是以犧牲速度為代價的。所以時鐘(頻率)管理的策略是,在保證電路主頻不變的情況下,通過多頻率技術,即在不同系統(tǒng)部分中

評論