基于AD9650的高速數據采集系統的設計方案

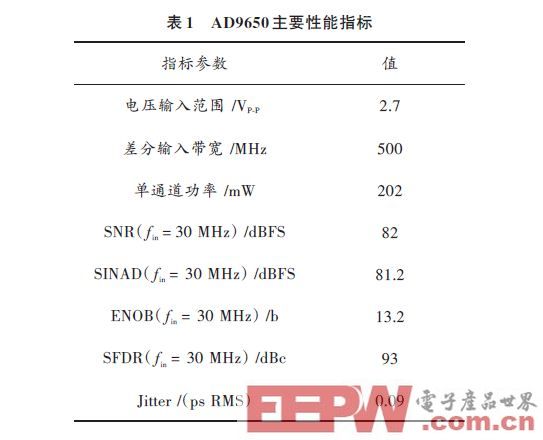

模數轉換模塊是信號采集系統最重要的組成部分。它主要包括ADC、前端電路和時鐘電路等。主要完成的功能是實現對模擬中頻輸入信號的數字化,以用于后續的數字信號處理。

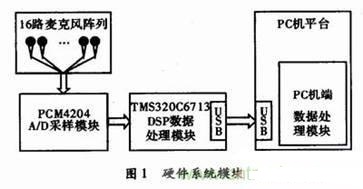

數字信號預處理模塊采用較為成熟的FPGA+DSP結構,主要實現對數字信號的FFT、數字正交解調等,同時實現對原始數據傳輸。信號預處理主要在DSP中完成,而FPGA內部搭建兩個FIFO來實現數據傳輸,同時完成對收發單元等的控制功能。FPGA采用Xilinx的低功耗高性能產品Spartan6,DSP 采用Analog Device公司的低功耗DSP產品ADSP21479.

數據傳輸模塊采用Cypress 公司的CY7C68014,通過USB 接口完成由FPGA 向嵌入式單板機的數據傳輸。嵌入式單板機具備各種符合計算機協議的數據接口,包括與電子硬盤的存儲接口,與上位機的網絡通信接口,以及與預處理卡的USB通信接口。

數據采集系統硬件電路實物,如圖7所示。系統分成兩塊電路板,即模擬ADC板和FPGA+DSP數字板,兩者通過PMC插件連接。

4 結語

本文研究了影響數據采集系統動態范圍的關鍵因素,給出了在采集系統設計時選擇芯片、設計時鐘和前端電路的依據,以此為基礎提出了一種高速數據采集系統的設計方案。論證分析表明,該設計方案能夠滿足雷達數據采集系統高速大動態范圍的要求。

評論