L-DACS1 中多速率卷積編碼器的設(shè)計(jì)與FPGA 實(shí)現(xiàn)

引言

本文引用地址:http://www.104case.com/article/227094.htm為了解決地-空的數(shù)據(jù)傳輸業(yè)務(wù)增長而帶來的高通信速度要求和高寬帶要求問題,國際民航組織(ICAO)要求民航通信從航空電報(bào)專用網(wǎng)絡(luò)向新一代航空電網(wǎng)過渡.因此歐洲EUROCONTROL 提出了未來航空通信系統(tǒng)(FAC),即L 波段數(shù)字航空通信系統(tǒng)類型1和2(L-DACS1 和L-DACS2),利用L波段(960~1 164 MHz)構(gòu)建新的地-空無線數(shù)據(jù)鏈路,提高數(shù)據(jù)傳輸速度,替代之前的窄帶通信系統(tǒng).

在L-DACS1 中,由于信道的噪聲和畸變與多普勒頻移的影響,會(huì)對傳輸?shù)男畔⒁鹗д婧托盘柵袥Q錯(cuò)誤,而且不同類型的數(shù)據(jù)需要采用不同的速率傳輸,因此需要使用多速率的信道編碼來降低誤碼率.卷積編碼是廣泛使用的信道編碼技術(shù),具有一定克服突發(fā)錯(cuò)誤的能力,可以降低信道的誤碼率,帶來很高的編碼增益.

因而多速率的卷積編碼是目前L-DACS1 中重要的組成部分.

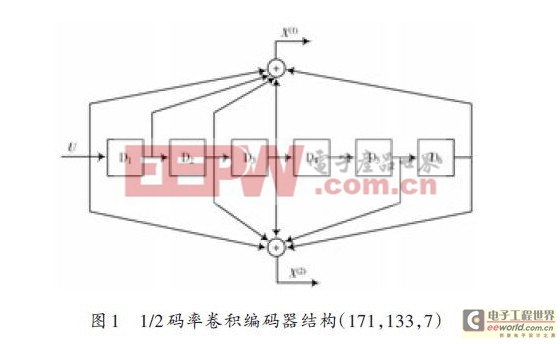

1 多速率卷積譯碼器原理卷積碼通常用(n,k,N)表示.其中k 表示輸入編碼器的數(shù)據(jù)位數(shù);n 表示編碼器輸出的數(shù)據(jù)位數(shù);N 為編碼約束長度,R = k n是卷積碼的碼率.L-DACS1 協(xié)議中采用(2,1,7)結(jié)構(gòu)的主題:卷積編碼,其生成多項(xiàng)式為[177,133],使用三種碼率分別是R=1/2,2/3,3/4.

L-DACS1 中使用的碼率R=1/2的卷積編碼器結(jié)構(gòu)如圖1所示.圖1中,D1D2D3D4D5D6 表示編碼器的狀態(tài)索引;U 表示輸入數(shù)據(jù)比特;X(1)X(2)表示輸出數(shù)據(jù)比特.

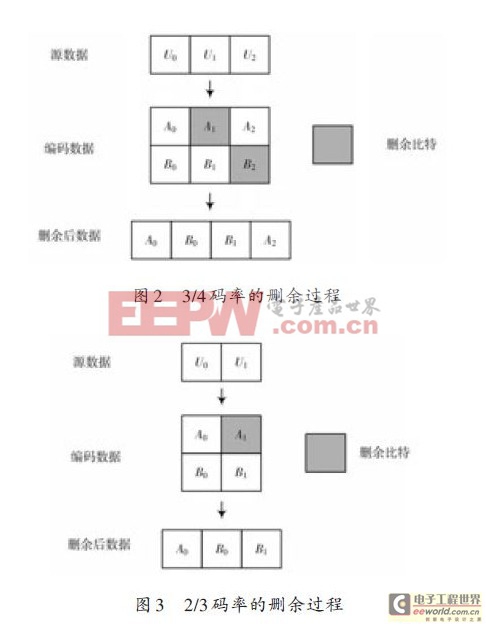

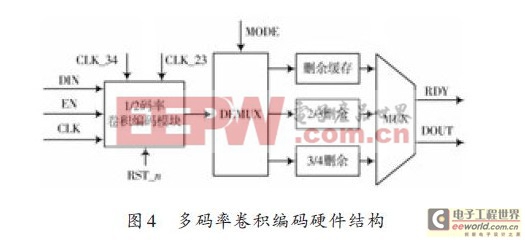

L-DACS1 基帶信號處理中,為了實(shí)現(xiàn)更高的速率和多種不同的傳輸速率,需要在1/2碼率卷積編碼的基礎(chǔ)上采用刪余操作,來實(shí)現(xiàn)多碼率的卷積編碼功能.3/4碼率的刪余過程如圖2 所示,2/3 碼率刪余過程如圖3所示.

圖2中,3/4碼率的刪余過程是每輸入3 b數(shù)據(jù),編碼為6 b的數(shù)據(jù),刪除固定位置的2 b,最終產(chǎn)生碼率為3/4的卷積碼[8].

圖3 中,2/3 碼率的刪余過程是每輸入2 b 數(shù)據(jù),編碼為4 b的數(shù)據(jù),刪除固定位置的1 b,最終產(chǎn)生碼率為2/3的卷積碼.

2 多速率卷積編碼器的設(shè)計(jì)與實(shí)現(xiàn)多速率卷積編碼模塊,根據(jù)主控單元輸出的模式信號(MODE)來控制數(shù)據(jù)的傳輸碼率,決定數(shù)據(jù)是否要進(jìn)入刪余處理以及進(jìn)入哪個(gè)刪余處理單元.

圖4 為多碼率卷積碼在L-DACS1 中硬件實(shí)現(xiàn)結(jié)構(gòu)圖.

表1為多速率卷積編碼器模塊端口說明.

表1為多速率卷積編碼器模塊端口說明.

圖4顯示給出的多速率卷積編碼器工作流程如下:數(shù)據(jù)在CLK時(shí)鐘的驅(qū)動(dòng)下以串行比特流的形式輸入1/2碼率的卷積碼模塊中進(jìn)行編碼處理,該卷積編碼模塊以同步的方式工作,每輸入1 b將會(huì)并行輸出2位編碼數(shù)據(jù),根據(jù)MODE控制信號,判斷1/2碼率卷積后數(shù)據(jù)進(jìn)行何種刪余操作,以實(shí)現(xiàn)3/4或2/3的碼率.

若采用1/2碼率編碼,由于后續(xù)模塊的實(shí)現(xiàn)算法是需要數(shù)據(jù)串行輸入,因此需要進(jìn)行并/串轉(zhuǎn)換,同時(shí)將時(shí)鐘提高至2×CLK_.為此需要增加一個(gè)2位的并入串出型緩存單元即刪余緩存單元.若采用2/3和3/4碼率編碼,經(jīng)過1/2碼率的卷積編碼模塊處理后,根據(jù)MODE信號把數(shù)據(jù)放入相應(yīng)的刪余緩存進(jìn)行刪余操作,以達(dá)到所需的碼率.輸出時(shí)鐘CLK_23,CLK_34 分別為1.33×CLK和1.5×CLK.

3 多速率卷積編碼器仿真利用Verilog HDL硬件描述語言對多速率卷積編碼器進(jìn)行仿真[9],對工程文件進(jìn)行綜合.布線和仿真,以3/4碼率卷積編碼為例進(jìn)行分析,其后仿真結(jié)果如圖5所示.

圖5 中,MODE 是模式控制信號,可根據(jù)該信號來選擇不同的刪余方式.con_in為模塊的輸入數(shù)據(jù),每次連續(xù)輸入144 b數(shù)據(jù),先進(jìn)行1/2 碼率的卷積編碼,數(shù)據(jù)變?yōu)?88 b,由于模式信號MODE為1111,所以進(jìn)行3/4碼率的刪余操作,得到192 b的串行數(shù)據(jù),使用CLK_34時(shí)鐘將3/4碼率的卷積編碼數(shù)據(jù)從data_out_34端口輸出.

將仿真通過的工程文件使用ChipScope添加觀察信號采樣時(shí)鐘.觸發(fā)信號和待觀察信號后重新綜合.布局布線生成bit文件,下載到Xilinx公司的Virtex-5系列的XC5VLX110-F1153型號的芯片后用ChipScope進(jìn)行在線測試,采用主時(shí)鐘75 MHz,得到測試結(jié)果如圖6所示.

評論