非傳統MOSFET方案提高功率CMOS器件功效的方法

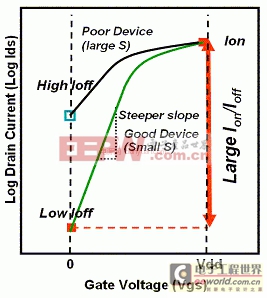

圖3:具有匹配的電流,但具有不同的亞門限斜率的兩個器件之間的亞門限行為。

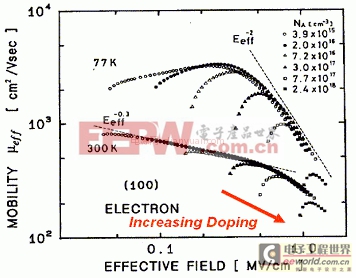

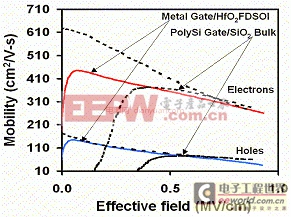

摻雜的另一個高代價是損傷傳輸速度。具有高溝道摻雜的器件被迫在更高門柵電場進行工作。這增加了具有門柵電介質界面溝道載流子的散射,導致載流遷移率(圖4)和折衷的驅動性能的大幅下降。

圖4:對于不同溝道摻雜水平(NA)和溫度[2], MOSFET的電子遷移率是有效電場的函數。

超薄體器件

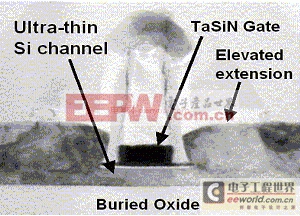

絕緣上硅(SOI)的異質結構為建造具有超薄硅體(硅厚度Tsi《10nm)(圖5)的器件創造了機會。通過由硅電介質界面建立的天然靜電屏障,超薄SOI提供一種控制短溝道效應的可選手段。由于受到超薄硅溝道的限制,源/漏結點深度現在就自然的變淺了。

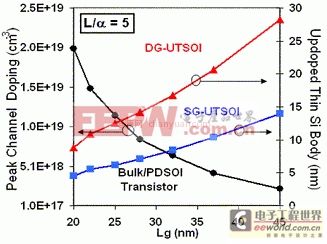

圖5所示為一個具有金屬門柵和高K門柵電介質的40nm-Lg全耗盡超薄(UT)SOI器件的透射電子顯微鏡(TEM)圖像。與體晶體管不同,超薄SOI通過它們的體結構來改進短溝道靜電效應,這一結構減少了它們對溝道摻雜的依賴(圖6)。要采用溝道摻雜工藝來控制最小體晶體 管中的漏電,防止其增長到不可控制的水平,這可通過采用薄Si來計算。由于損耗電容Cdm保持為最小值,通過減少S,可使得開/關電流的比率最大化 。

圖6 所示為體MOSFET與超薄(UT)SOI所需的溝道摻雜之間的比較,以為給定Lg實現相同的短溝道控制(SG:單一門柵,;DG: 雙門柵;PD-SOI: 部分損耗的SOI)。

由于具有低溝道摻雜或不具溝道摻雜,這樣一個器件的門限電壓可主要通過門柵和電介質材料來確定。由于等效的溝道損耗寬度?Wdm?比Tsi更大,因此, 溝道是完全損耗的。通過放棄使用溝道摻雜物來控制短溝道效應,完全損耗的SOI器件能在減少的有效電場進行操作,在此,載流子遷移率更高(圖7)。

圖7與等效的體晶體管相比,在具有更高遷移率的情況下,FD-SOI器件能以更低的有效電場工作。

取消溝道摻雜也減少了因隨機摻雜物波動引起的可變性。盡管在薄Si體厚度中有變化,與有摻雜體器件相比,FD-SOI器件顯示非常大地改進了器件與器件之間的匹配性能 (圖8)。這對于存儲容量不斷擴大的SRAM和受隨機變化影響的模擬技術而言則是非常重要的。

圖8: FD-SOI與其它來自不同工藝的等效器件之間的失配比較(PDSOI:部分損耗的SOI)。FD-SOI對浮體效應的免疫性和最小化源/漏(S/D)結電容(Cj)以及跟金屬

評論