采用創(chuàng)新降耗技術應對FPGA靜態(tài)和動態(tài)功耗的挑戰(zhàn)

可選核電壓

可選核電壓允許設計師根據性能需求采用0.9或1.1V核電壓。0.9V核電壓提供整體上最低的動態(tài)和漏電功耗;而1.1V核電壓提供整體上的最高性能。動態(tài)功耗與核電壓的平方成正比,而靜態(tài)功耗是核電壓的2.5次方。

在板卡設計時,可選核電壓輸入可被設定為0.9 V或1.1 V。該核電壓為核構造內的所有LAB、存儲器和DSP功能提供工作電源。可選核電壓影響構造性能,所以,若在軟件中選擇了器件和速度等級,則還需進行核電壓選擇。該軟件利用與所選核電壓相對應的時序和功耗模型來實現全部依賴時序和依賴功耗的分析和優(yōu)化。

當選擇采用哪種核電壓時,設計師必須考慮由時序分析得出的系統(tǒng)性能需求。若采用0.9 V就能滿足系統(tǒng)性能要求,則肯定比采用1.1 V所用的功耗低。

技術融合

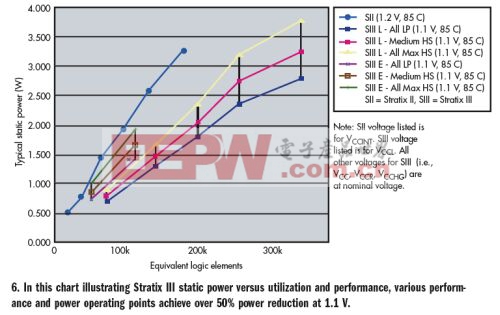

在1.1 V,將可編程電源技術和可選核電壓結合起來,可提供降耗50%以上的各種性能和功耗工作點(圖6)。基于所用的各種資源(如:DSP塊和TriMatrix存儲器塊),靜態(tài)功耗會顯著不同。

根據核電壓和高速邏輯與低功耗邏輯比例的不同,總合起來的靜態(tài)和動態(tài)功耗也各異。在許多設計中,當不需要FPGA的最高性能時,可將設計的整體功耗降低50%以上。

工藝和電路技術

半導體行業(yè)通過在設備、工藝技術、設計工具和電路技術方面的巨大投入一直在不懈地迎擊隨著工藝尺度的縮微所帶來的不斷挑戰(zhàn)。特別是業(yè)界面對的隨著工藝尺度的縮微而不斷增加的漏電流問題。因此,采用了在65nm(及更精微)工藝節(jié)點許多廣為人知的技術在保證或提升性能的同時來管理漏電功耗,這些技術有:銅布線、低k電介質、多閥值晶體管、可變柵長晶體管、三閘級氧化層、超薄柵氧化層、應變硅。

評論