基于高速幀同步和相位模糊估計法的FPGA實現

用Matlab仿真測試結果如下:在各個偏移相位下比特信噪比從6~20 dB,在未做前后方保護的情況下做104次仿真。有假同步概率為0;同步概率為1;失步概率為0。這樣加上系數為3的前后方保護后,相當于做1012次仿真。有假同步概率為0;同步概率為1;失步概率為0。由上可見,理論分析和仿真實驗得到的性能均滿足系統的要求。

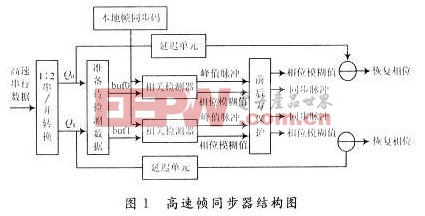

實際應用中符號速率為320 MSPS,8PSK調制信號的幀同步碼長為58,幀長為2 660個調制符號。整個結構流程描述如下:

(1)首先將320 MHz的接收數據進行1:2串/并轉換,將數據速率降低為160 MHz,得到Q0,Q1兩路并行數據。這樣保證了系統的主要功能模塊是較低速實現的,而只有少量接口模塊需要考慮高速問題。

(2)待檢測數據的準備

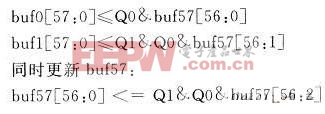

首先緩存串/并轉換前的57個數據,得到buf57。然后將該緩存數據與并行輸出數據Q0,Q1進行組合來形成58個待檢測數據。方法如下:

這樣就產生了2組各58個并行數據,用于與本地同步碼進行相關運算。

(3)將待檢測數據送入相關檢測器,使用簡化的相關算法和兩個門限的判決方法,可以得到峰值脈沖并估計出相位模糊值。

由于相關值的計算僅與接收符號和本地同步碼的相位有關,所以在FPGA實現時,可以以相位為地址,精心設計RAM,直接查表得到三角值。之后用IPcore生成加法器,對三角值求和得到相關值的實部和虛部。將相關值的實部和虛部分別與設定的threshold_0,threshold_1進行比較,以比較結果為地址,根據表1的判決邏輯設計RAM初始值。這樣就可根據比較結果直接查RAM得到峰值脈沖和相位模糊值。

評論