基于高速幀同步和相位模糊估計法的FPGA實現

當接收數據的幀頭部分與本地同步碼完全對齊時,可對式(5)做如下討論:

(1)若l=0,2,4,6,即相位模糊值為π/4的偶數倍,觀察式(5)可知,此時相關值僅包含實部或虛部。故實部或虛部的絕對值(相關值的模)應該大于判決門限,設為threshold_0。

(2)若l=1,3,5,7,即相位模糊值為π/4的奇數倍,觀察式(5)可知,此時相關值包含實部和虛部。實部和虛部的絕對值均約為相關值的模,所以它們的倍約為相關值的模,且都應該大于門限threshold_0。因此它們本身都應該大于

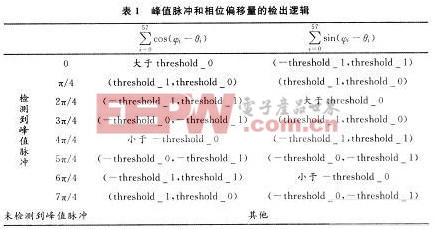

通過上述分析可知,相關檢測問題實際上可以轉化為相關值的實部和虛部與兩個門限進行比較的問題。其判斷邏輯如表1所示。

注:第二列為按照逆時針計算的相位模糊值。

式(3)表明,僅通過接收符號的相位以及本地同步碼的相位即可計算出相關值的實部和虛部。

之后將實部和虛部分別與兩個門限值做比較,然后根據表1的判決邏輯,即可直接檢測出峰值脈沖與相位模糊值。

3 算法性能分析

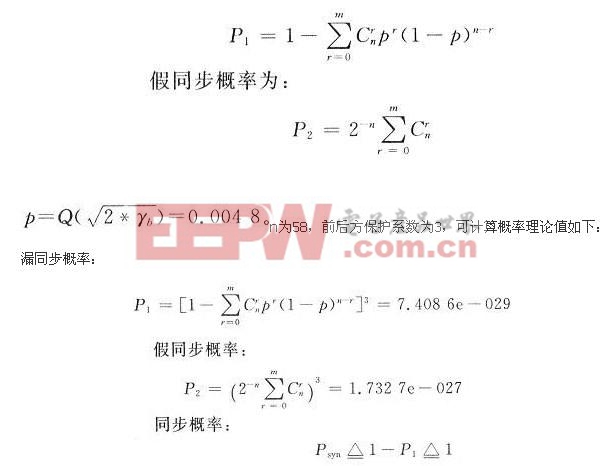

幀同步系統應有較強的抗干擾能力,通常用漏同步概率、假同步概率來衡量其系統性能。本文的方法應用在320 MHz符號速率8PSK信號系統的幀同步和相位模糊值的估計上。其中,幀同步碼長為58;幀全長為2 660個調制符號。并且要求在比特信噪比不低于6 dB的情況下,漏同步概率小于10-12;假同步概率小于10-12;同步概率大于0.95。

設p為碼元錯誤概率,n為同步碼組的碼元數,m為判決器容許碼組中的錯誤碼元最大數,則漏同步概率為:

這是滿足系統要求的。

評論