基于FPGA的絕對(duì)式編碼器通信接口設(shè)計(jì)

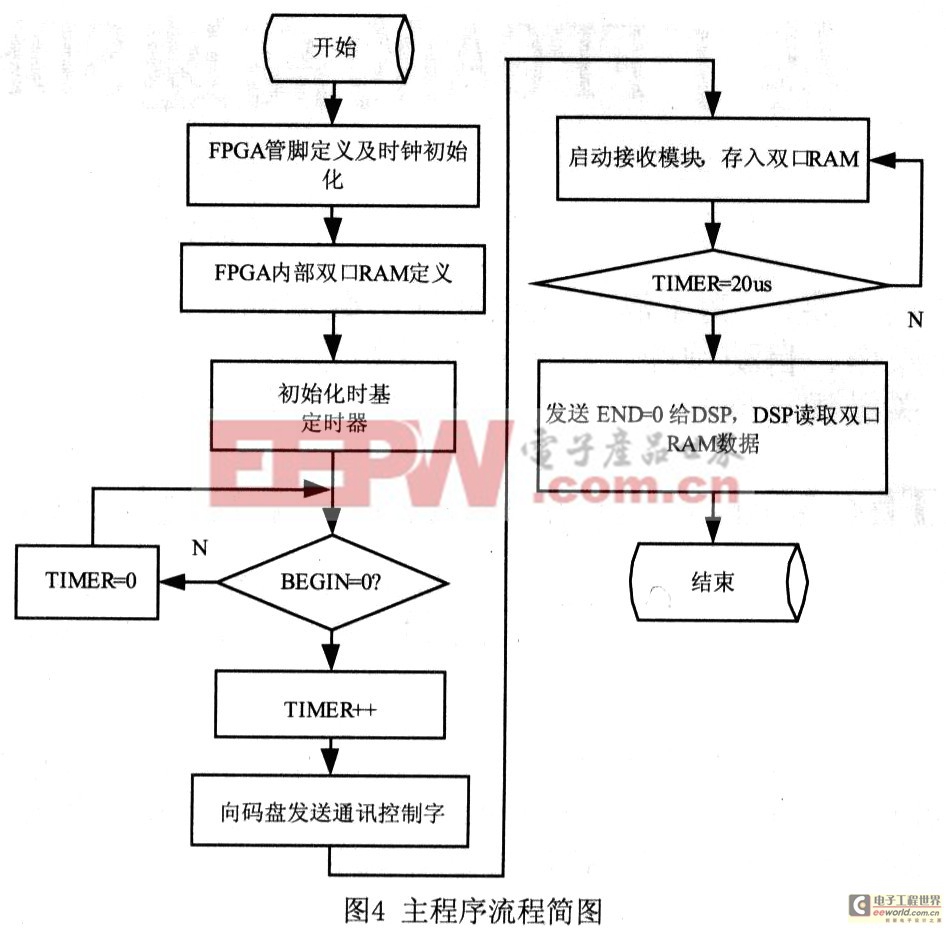

在本接口的研發(fā)過程中,對(duì)FPGA的開發(fā)采用Altera公司的Quartus II 5.1集成環(huán)境,硬件描述語言為VHDL語言。圖4為主程序流程圖。

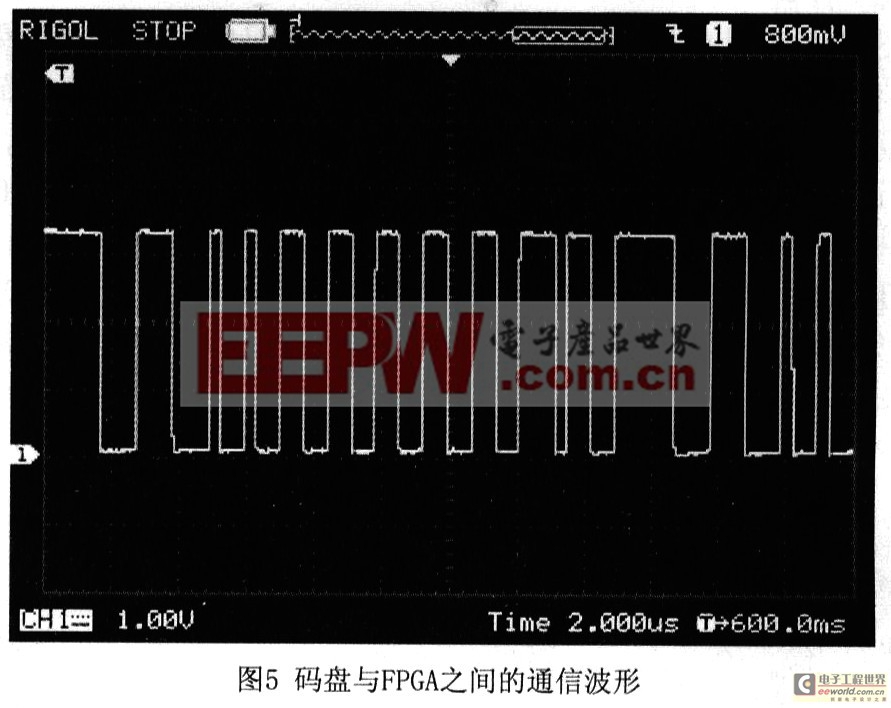

圖5為碼盤與FPGA之間的通信波形,從位置信號(hào)可以看出該接口工作正常。

3 結(jié)束語

本文設(shè)計(jì)了一種基于FPGA的絕對(duì)式碼盤智能接口,用以進(jìn)行絕對(duì)式編碼器和伺服驅(qū)動(dòng)器DSP處理器之間的通信。并且具CRC校驗(yàn)等糾錯(cuò)功能。該接口基本可以替代價(jià)格昂貴的專用接口芯片,降低產(chǎn)品的成本,促進(jìn)伺服電機(jī)驅(qū)動(dòng)器的國產(chǎn)化進(jìn)程。

評(píng)論