基于FPGA的絕對式編碼器通信接口設計

2 絕對式編碼器接口的實現

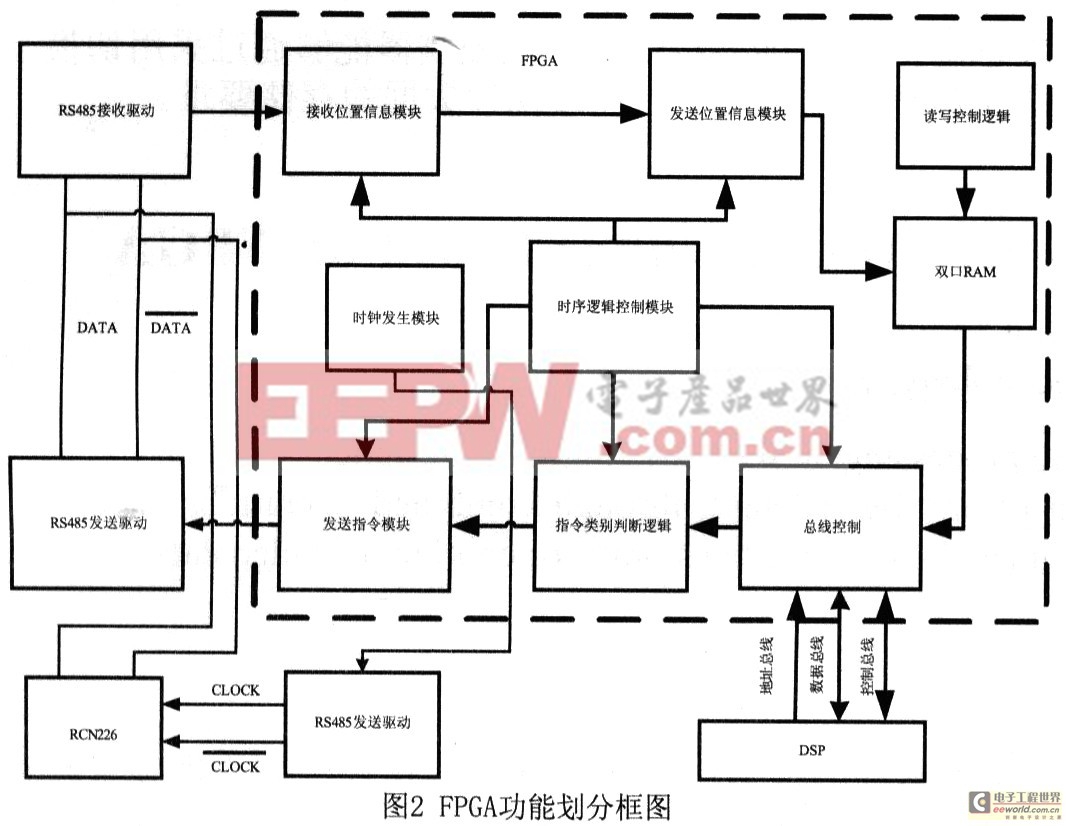

全數字化交流伺服系統中采用TMS320X2812作為控制器,用以實現位置環、速度環和電流環以及SVPWM、電壓和電流采樣等功能。此外,采用Altera公司的型號為FP1C6的~Cyclone系列FPGA,用以實現與絕對式碼盤接口、譯碼邏輯等功能。同時,在FPGA內部實現了256字節的雙口RAM,用來與DSP之間通過總線實現數據傳輸。FPGA部分的功能框圖如圖2P所示。

碼盤接口部分分為發送模塊、接收模塊、雙口RAM模塊、主程序模塊四部分。由于每次通信時間是嚴格固定的,設系統時鐘為2MHz。FPGA為主叫,向編碼器發送"請求數據"控制字共6位,需時3 μs,編碼器向FPGA共發送1個起始位、兩個"錯誤位"、26位位置值和5位CRC校驗位,共34位的數據共需時17 μs,所以每次通信需要20 μs的時間,并且每個時刻具體需要傳遞哪一位數據也是嚴格確定的。因此采用基于時基的設計方法。

FPGA內部設計了一個時基為20ns的計數器,每20ns加1,作為整個電路的時基,根據這個時基來確定每一時刻收到的數據具體屬于哪個位。在FPGA 內部實現了256bytes的雙口RAM空問,A口具有8位數據線,8位地址線,用于與編碼器通信,B口具有16位數據線,8位地址線,用于與DSP通信,因為TMS320X2812為16位DSP,所以與FPGA中RAM的數據傳遞極為方便。

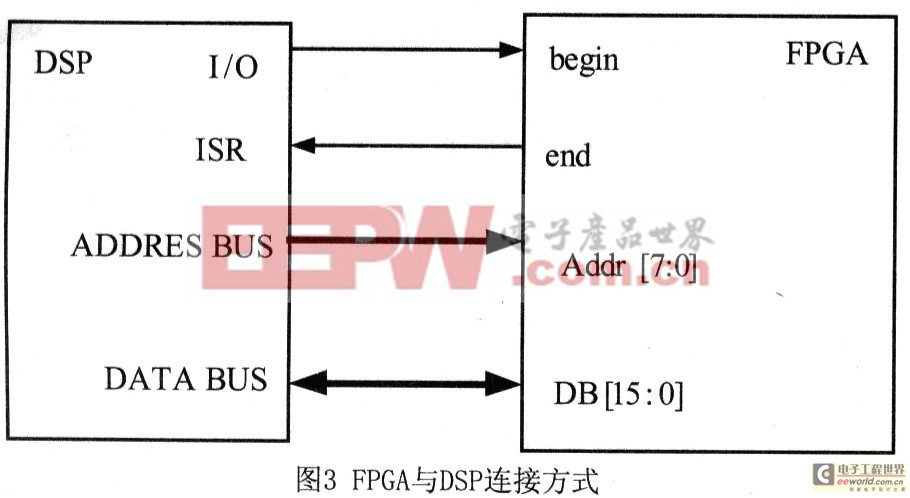

DSP在每個電流環周期發送一個有效的"begin"信號,20μs之后,碼盤信號接收模塊將接收到的數據存入FPGA內部雙口RAM的A口中,并按順序排列成16位數據的形式,然后向DSP發送end信號,表示一次通信結束,DSP接收到中斷之后從FPGA的雙口RAM的B口中讀取數據,完成一次通信, DSP的連接如圖3所示。

評論