一種基于FPGA的新型數字電壓表研究與設計

4.2 信號采樣周期自調整算法

為協調好數據精度和系統負擔兩者之間的關系,對于疊加周期信號的輸入信號Vi,規定單個周期的數據采集不少于8個點,因此要對AD0809的采樣周期進行自適應調整。這里使用過零點檢測的方法,如果疊加信號的周期在0~25 Hz范圍內,采樣周期為5 ms。疊加信號周期在25~50 Hz時,采樣周期為2 ms;疊加信號周期在50~100 Hz時,采樣周期為1 ms。

設采樣周期的初始值為2 ms,采樣數為100點。則有:首先采集100個數據,計算平均值,作為輸入信號Vi的均估值(平均值的估計值);再采集100個數據,與Vi的均估值進行比較,計算過零點的數量并統計;根據此數量,調整采樣周期,當此數量大于20時,令采樣周期為1 ms。當此數量不大于10時,令采樣周期為5 ms。其他令采樣周期為2 ms。

4.3 檢測疊加信號周期算法

依舊采用檢測過零點的數目來檢測周期。

設采集的數據點為1O0個,計算均值,作為輸入信號Vi的均估值;再采集數據,與Vi的均估值進行比較,計算過零點的數量并統計,同時統計每個數據過零點的時刻;檢測到三個過零點時,判斷其是否符合均勻分布,判斷是否檢測到一個周期。若檢測到一個周期,則停止檢測并計算此周期,否則繼續檢測。若檢測到相當數量的數據點,過零點數量仍小于3個,則認為輸入信號為直流信號。

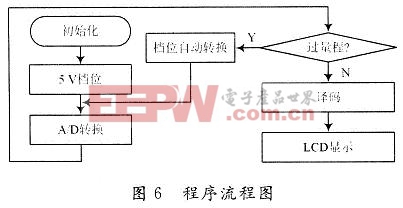

5 程序流程

程序流程如圖6所示。

6 測試結果分析

采用高精度數字多用表UT88B輸出值作為標準值。由表1所示。

由數據對比可以看出,在O~5 V檔位上,該數字電壓表的誤差基本在O.01 V內。在O~50 V檔位上,誤差有所增大,但也控制在O.02 V以內,體現了ADC0809的轉換精度,電路整體設計合理可靠。至于O.02 V以內的偏差,可修改程序,采用軟件的方法進行數據校正,也可以進一步校正A/D的基準電壓。

7 結語

利用現場可編程門陣列技術,設計了該新型數字式電壓表。用軟件替代諸多硬件,在一塊高性能FPGA芯片上,實現采樣時序的控制、檔位的判斷選擇、碼制的轉換和LCD驅動,極大地提高了系統集成度和可靠性。文中重點介紹了檔位電路和FPGA內部模塊的設計以及關鍵算法的實現步驟。由測試結果,可看出該儀表測量范圍較寬,測量精度較高,能夠滿足物理實驗中電量的測量要求。經實際使用證明,系統運行穩定、操作方便。為了方便電壓表系統與計算機直接通信,還可進一步增加RS 232接口,進行電平轉換,可將測得的數據實時導入計算機中使用。

評論