基于FPGA和VHDL的USB2.0控制器設計

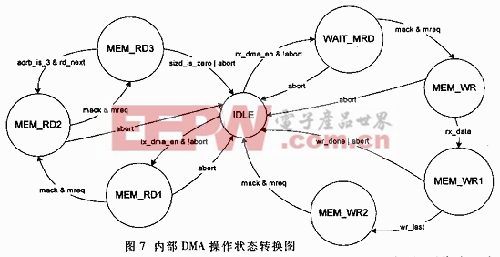

由于USB2.0協議定義的事務操作以8bit為單位,因此完成一次32bit的DMA操作需要進行4次寫8bit。內部DMA采用高效的One-hot狀態機設計方法,狀態轉換如圖7所示。當需要將接收到的數據存儲到SRAM(rx_dma_en=1)時進入WAIT_MRD狀態,在該狀態選中一個臨時數據寄存器,并向存儲器發送請求信號mreq,從存儲器中預取4字節(當接收到的數據少于4字節時,保證有4字節的數據寫入存儲器)到該寄存器中,然后進入MEM_WR狀態。當PL的分組拆裝器接收到1字節數據時,將該字節寫入臨時存儲器,轉入下一狀態MEM_WR1;當分組拆裝器沒數據給DMA仲裁器時則進入MEM_WR2狀態,在此狀態將臨時存儲器中的數據寫入SRAM,然后回到IDLE狀態。在操作過程中,使用計數器adr_cb對傳輸字節數進行計數,通過addr_cb[1:0]的值標識當前傳輸的是32bit中的哪個字節。計數器sizu_c每接收1字節數值加1。

在需要讀取SRAM中的數據(tx_dma_en=1)時,DMA仲裁器由IDIE狀態進入MEM_RD1狀態,讀取4字節數據到發送緩沖區中,然后進入狀態MEM_RD2,再讀4字節進入狀態MEM_RD3,這8字節輪流使用Buffer0和Buffer1緩沖區:

在需要讀取SRAM中的數據(tx_dma_en=1)時,DMA仲裁器由IDLE狀態進入MEM_RD1狀態,讀取4字節數據到發送緩沖區中,然后進入狀態MEM_RD2,再讀4字節進入狀態MEM_RD3,這8字節輪流使用Buffer0和Buffer1緩沖區:

if((NOT adr_cb[2]) AND mack

then Buffer0=SRAM_DATA_I;

elsif (adr_cb[2] AND mack)

then Buffer1=SRAM_DATA_I;

end if;

在MEM_RD3狀態判斷是否還需要讀下一個數據,如果需要再進入狀態MEM_RD2,否則在傳輸完所有字節后,返回到IDLE狀態。在發送數據過程中,使用14bit計數器sizd_c決定傳輸字節數,取自Ep_BUF[30:17],每發送1字節數據,它的值減1。在圖7中的各個狀態中,由于超時、CRC校驗錯誤或得到的數據發生錯誤時,PE產生的Abort信號會使當前狀態都回到IDLE。

文中闡述了USB2.0功能控制器的一種實現方案。 其VHDL語言實現代碼,已在XILINX公司的FPGA Virtex XVV3006fg456中通過了Xilinx ISE的仿真、綜合及布局布線。FPGA的規模是32萬門,1536個CLB(可配置邏輯單元)。該控制模塊占用2050個Slice(66%),使用了1697個Slice觸發器(27%)和3047個4輸入LUT表(49%)。整個FPGA的速度可達到56.870MHz,完全滿足視頻數據的高速傳輸(對32bit數據操作,達到480Mb/s的速度時鐘只需15MHz)。該方案實現的控制器便于修改且易于實現,可作為一個功能模塊嵌入到SOC中,可使不同情況最大限度地靈活設計片上系統。

評論