基于FPGA和VHDL的USB2.0控制器設計

在視頻存儲和圖像寬帶領域中,經常遇到實時高速數據傳輸的要求。2000年4月,由Intel、Microsoft、NEC、Compaq、Lucent、Phillips等公司共同制訂的USB2.0(Universal Serial Bus)傳輸協議,其速度遠遠超過了目前使用IEEE1394接口進行視頻傳輸的400Mbps,達到了480Mbps;而且具有即插即用的PnP(Plug And Play)、可進行菊花鏈式的級聯(通過USB HUB進行外圍擴展)、可串連多達127個USB設備等優點。應用該協議可支持實時語音、音頻和視頻數據的傳輸。

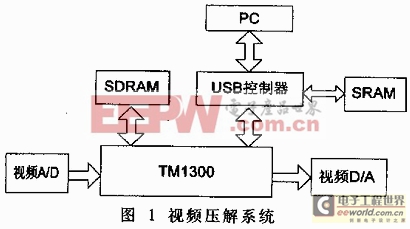

本文針對高速數據傳輸需求,根據USB2.0的協議規范,利用VHDL語言實現符合該協議的功能控制器,在視頻壓解系統中使數據在PC與外設之間高速傳輸。如圖1所示由視頻A/D采集的原始視頻數據,在Philips公司生產的TM1300專用視頻處理器中壓縮后,通過USB控制器送至PC機。PC機的整個通過USB控制器傳輸到TM1300,解壓后發送至視頻D/A。

1 控制器結構原理

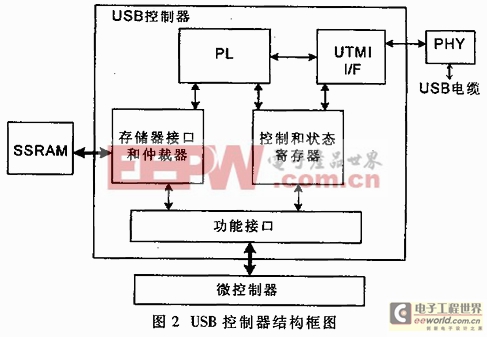

USB2.0控制器結構框圖如圖2所示。控制器主要由兩個部分組成,其一為與外設的接口,另一個是內部協議層邏輯PL(Protocol Layer)。內部存儲器仲裁器實現對內部DMA和外部總線對存儲器訪問之間的仲裁。PL則實現USB的數據I/O和控制。

接口有三種:一種是與微控制器之間的功能接口;一種是與單口同步靜態存儲器(SSRAM)之間的接口;另外一種是與物理層之間的接口。這里符合UTMI(USB Transceiver Macrocell InteRFace)規范定義。

評論