基于FPGA和VHDL的USB2.0控制器設(shè)計(jì)

2.2 協(xié)議層

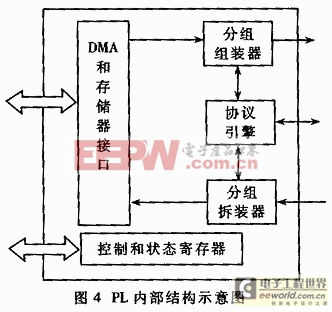

控制器的核心邏輯位于PL(Protocl Layer)模塊,負(fù)責(zé)管理所有USB數(shù)據(jù)I/O和控制通信,其結(jié)構(gòu)如圖4所示。

DMA和存儲(chǔ)器接口提供隨機(jī)存儲(chǔ)器訪問和DMA操作。該模塊使PL和外部微控制器采用DMA方式訪問SSRAM。當(dāng)外部總線有訪問SRAM的請(qǐng)求時(shí),且PL沒有請(qǐng)求訪問存儲(chǔ)器,控制邏輯如下:req、ack分別對(duì)應(yīng)外部總線和存儲(chǔ)器之間的請(qǐng)求和響應(yīng)信號(hào),din、addr和we分別是外部總線給出的數(shù)據(jù)、地址和寫信號(hào),mreq是內(nèi)部DMA向存儲(chǔ)器發(fā)送的請(qǐng)求信號(hào),mdin、maddr和mwe分別是內(nèi)部DMA給出的數(shù)據(jù)、地址和寫信號(hào)。

sel =(req OR ack_r) AND(NOT mreq);

if sel='1' then

sram_out=din;

sram_adr=addr;

sram_we=req AND we;

else

sram_out=mdin;

sram_adr=maddr;

sram_we =mwe;

end if;

由控制邏輯可看出,內(nèi)部DMA操作的優(yōu)先級(jí)比外部總線高。

協(xié)議引擎(Protocol Engine)處理所有標(biāo)準(zhǔn)的USB握手信號(hào)和控制通信。分組組裝器組裝分組并送入輸出FIFO,先組裝分組頭,插入適當(dāng)?shù)腜ID(分組標(biāo)識(shí))和校驗(yàn)和,然后加入數(shù)據(jù)域。分組拆裝器先解碼出PID和序列號(hào)以及校驗(yàn)和,再從8位PID取低4位(或高4位取反)得到PID[3:0],通過USB2.0協(xié)議的PID類型定義譯碼出PID名,判斷是Token分組(OUT、IN、SOF和SETUP)還是DATA分組(DATA0、DATA1、DATA2和MDATA)。

Pid_Token=pid_OUT OR pid_IN OR pid_SOF OR pid_SETUP;

Pid_DATA =pid_DATA OR pid_DATA1 OR pid_DATA2 OR pid_MDATA;

如果是Token分組(格式定義如圖5所示),則將后續(xù)的16bit數(shù)據(jù)分別放入兩個(gè)8bit臨時(shí)Token寄存器token0和token1,然后取出分組中的7位地址、4位端點(diǎn)號(hào)及5位CRC校驗(yàn)碼。

Token_fadr=token0[6:0];

Token_endp=token1[2:0] token0[7];

Token_crc5=token1[7:3];

對(duì)于特殊的Token須進(jìn)行特殊的處理,本文實(shí)現(xiàn)的控制器只對(duì)SOF這一特殊Token進(jìn)行操作,解出PID后的11位幀號(hào)及5位CRC5校驗(yàn)碼。

Frame_no=token1[2:0] token0;

Token_crc5=token1[7:3];

檢驗(yàn)校驗(yàn)碼是否出錯(cuò),如果出錯(cuò)等待下一個(gè)Token,否則將地址、端點(diǎn)號(hào)和幀號(hào)等放入相應(yīng)寄存器。Token類型如果是IN,則執(zhí)行組裝分組并發(fā)送寄分組;如果是OUT則拆卸接收到的數(shù)據(jù)分組。對(duì)于其他不支持的Token則視為錯(cuò)誤處理:Pid_ERROR=pid_ACK OR pid_NACK OR pid_STALL OR pid_NYET OR pid_PRE OR pid_ERR OR pid_SPLIT OR pid_PING;如果出錯(cuò)則不進(jìn)行Token的解碼,而等待下一個(gè)Token的到來。

如果是DATA分組,則緊接著PID的是最大載荷為1024字節(jié)的數(shù)據(jù)和16位CRC16校驗(yàn)碼。對(duì)數(shù)據(jù)的處理先寫入端點(diǎn)寄存器,然后通過DMA操作寫入SSRAM。下面詳細(xì)介紹端點(diǎn)寄存器和DMA操作。

評(píng)論