可重構(gòu)技術(shù)及基于FPGA的可重構(gòu)智能儀器設(shè)計(jì)

2.4 外圍電路設(shè)計(jì)

外圍電路設(shè)計(jì)包括存儲(chǔ)器設(shè)計(jì)、AD 轉(zhuǎn)換電路設(shè)計(jì)、DA 轉(zhuǎn)換設(shè)計(jì)、顯示電路設(shè)計(jì)、開 關(guān)量DI、DO 設(shè)計(jì)和RS232 通信設(shè)計(jì)等。

儀器上的存儲(chǔ)器包含 1 片8M 字節(jié)的SDRAM 和一片32M 字節(jié)的FLASH 存儲(chǔ)器。限于 篇幅SDRAM(IS42S16400)與EP2C35F672C6 連接的引腳、FLASH 存儲(chǔ)器(AT49BV163) 與EP2C35F672C6 連接的引腳分配這里不再贅述。

A/D 轉(zhuǎn)換電路采用了AD7810 芯片、DA 轉(zhuǎn)換電路采用AD5611 芯片。

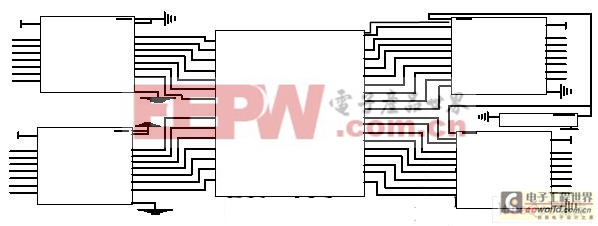

DI、DO 均為16 路,數(shù)字端口滿足標(biāo)準(zhǔn)TTL 電氣特性。數(shù)字量輸入最低的高電平為2V, 數(shù)字量輸入最高的低電平為0.8V;數(shù)字量輸出最低的高電平為3.4V,數(shù)字量輸出最高的低 電平為0.5V。DI、DO 部分的電路如圖4 所示:

3 可重構(gòu)智能儀器軟件設(shè)計(jì)

3.1 可重構(gòu)儀器軟件結(jié)構(gòu)

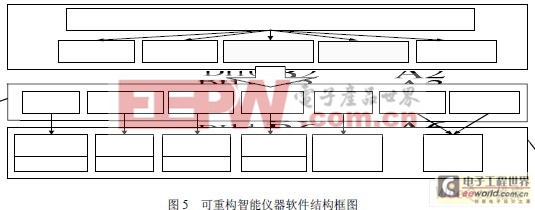

可重構(gòu)智能儀器的軟件結(jié)構(gòu)如圖5 所示。

系統(tǒng)軟件模塊庫(kù):包含軟件控制模塊、RS232 通訊模塊、模數(shù)轉(zhuǎn)換模塊、數(shù)模轉(zhuǎn)換模塊、 顯示模塊和DI、DO 開關(guān)量模塊。通過軟件控制模塊選擇其他的模塊進(jìn)行組合就可以實(shí)現(xiàn)不 同的軟件功能,從而達(dá)到重構(gòu)的目的。

HAL 程序庫(kù)實(shí)際上包含了各種不同的硬件驅(qū)動(dòng),包括MAX232 驅(qū)動(dòng)、AD 轉(zhuǎn)換芯片驅(qū) 動(dòng)、DA 轉(zhuǎn)換芯片驅(qū)動(dòng)、FPGA 的I/O 引腳驅(qū)動(dòng)等。

通過選擇軟件模塊庫(kù)中的軟件模塊,就可以調(diào)用 HAL 程序庫(kù)中相應(yīng)的硬件驅(qū)動(dòng),從而 實(shí)現(xiàn)上層應(yīng)用程序?qū)Φ讓佑布目刂啤\浖K的可重構(gòu)性對(duì)應(yīng)了底層硬件的可重構(gòu)性。

評(píng)論