基于FPGA實(shí)現(xiàn)的SCI接口電路IP核的設(shè)計(jì)

仿真結(jié)果

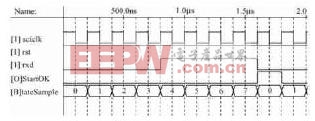

圖6 起始位檢測仿真波形

由圖7仿真波形可知,采樣一位數(shù)據(jù)的狀態(tài)機(jī)在數(shù)據(jù)位的第4、5、6個內(nèi)部sclk時鐘進(jìn)行。位值由多數(shù)采樣的值決定,圖中rxd在第4、5、6圖7 采樣一位數(shù)據(jù)的仿真波形個sclk時的值為1,故dok在第8個sclk時鐘輸出1,表示此次采樣的一位數(shù)據(jù)為1。

圖7 采樣一位數(shù)據(jù)的仿真波形

結(jié)論

SCI接口電路由VerilogHDL語言描述,可讀性好,便于修改與測試,可方便地嵌入到用戶的FPGA系統(tǒng)。筆者利用Xilinx公司的Spartan ⅡFPGAXC2S100成功地實(shí)現(xiàn)了FPGA與PC機(jī)的串行通信。如在此基礎(chǔ)上增加其它的控制寄存器,則可設(shè)計(jì)出功能更為完善的SCI接口電路。

評論