基于FPGA的寬帶數(shù)字接收機(jī)變帶寬數(shù)字下變頻器

2 窄帶濾波器組模塊

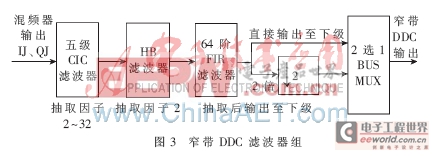

窄帶濾波器組模塊基于傳統(tǒng)數(shù)字下變頻結(jié)構(gòu),其內(nèi)部框圖如圖3所示。為了實(shí)現(xiàn)濾波器組處理帶寬可變,HB及FIR濾波器的濾波器系數(shù)均可變,并且CIC濾波器的抽取因子可以在2~32范圍內(nèi)靈活選擇,F(xiàn)IR濾波器輸出后也可選擇直接輸出至下級(jí)或者2倍抽取后輸出至下級(jí)。這樣窄帶濾波器組總的抽取因子可在4~128范圍內(nèi)變化,即可根據(jù)信號(hào)處理帶寬使輸出數(shù)據(jù)率在25 MS/s~0.781 25 MS/s之間靈活改變,實(shí)現(xiàn)窄帶VB-DDC的功能。

3 多相濾波結(jié)構(gòu)的寬帶濾波器

在本設(shè)計(jì)中,當(dāng)信號(hào)帶寬大于1 MHz時(shí),由寬帶濾波器處理。AD采樣率100 MS/s時(shí),設(shè)計(jì)寬帶濾波器:通帶0.5 MHz,阻帶起始頻率1.8 MHz,通帶波紋0.1 dB,阻帶抑制比為84 dB,調(diào)用MATLAB中函數(shù)firpm設(shè)計(jì)濾波器,計(jì)算所需的濾波器階數(shù)為266。

為了實(shí)現(xiàn)266階的FIR濾波器,采用基于多相濾波的乘法器時(shí)分復(fù)用結(jié)構(gòu)。多相因子取38,抽取因子取7。

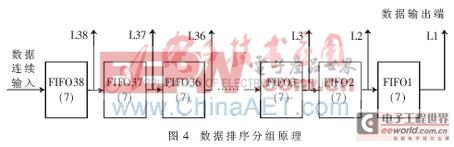

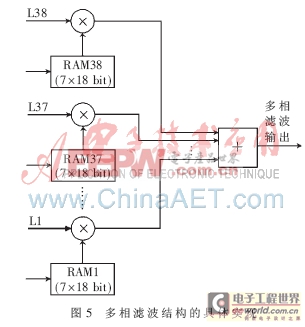

數(shù)據(jù)排序分組原理如圖4所示,其中FIFO1~FIFO38的38個(gè)獨(dú)立的存儲(chǔ)器用38個(gè)深度為7、位寬為18的FIFO實(shí)現(xiàn)。FIFO的個(gè)數(shù)由多相因子決定,為了實(shí)現(xiàn)處理帶寬可變,輸出信號(hào)數(shù)據(jù)率可變,抽取因子可在1~7之間選擇,F(xiàn)IFO的深度由抽取因子決定,可在1~7之間配置。由L1~L38輸出的數(shù)據(jù)應(yīng)乘以對(duì)應(yīng)的濾波器系數(shù),然后將這38個(gè)乘積累加,則可得到多相濾波的輸出,如圖5所示。

MATLAB產(chǎn)生266階原型低通濾波器系數(shù),通過參數(shù)配置模塊在DDC開始工作前存入RAM中,在參數(shù)配置模塊中有專門的RAM寫操作控制邏輯。由于抽取因子可在1~7之間靈活配置,則濾波器總的階數(shù)可在138~738,即38~266之間變化,所以RAM中預(yù)存的濾波器系數(shù)應(yīng)根據(jù)濾波器實(shí)際階數(shù)靈活配置,多余的RAM存儲(chǔ)空間置零。

評(píng)論