一種基于FPGA的復(fù)數(shù)浮點協(xié)方差矩陣實現(xiàn)

2 仿真結(jié)果

可編程邏輯設(shè)計有許多內(nèi)在規(guī)律可循,其中一項就是面積和速度的平衡與互換原則。面積和速度是一對對立統(tǒng)一的矛盾體,要求一個設(shè)計同時具備設(shè)計面積最小,運行頻率最高,這是不現(xiàn)實的。于是基于面積優(yōu)先原則和速度優(yōu)先原則,本文分別設(shè)計了協(xié)方差矩陣的串行處理方案和并行處理方案,并用Altera\stratix\EP1S20F780C7進行板上調(diào)試。其調(diào)試結(jié)果表明,串行處理方案占用的資源是并行處理方案的1/4,但其運算速度卻是后者的11倍。

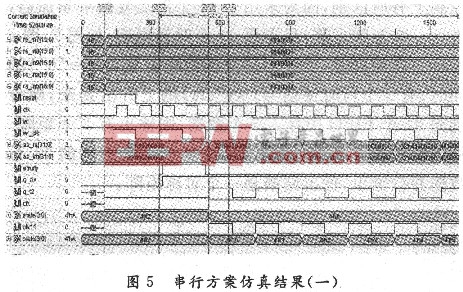

2.1 串行處理方案仿真結(jié)果

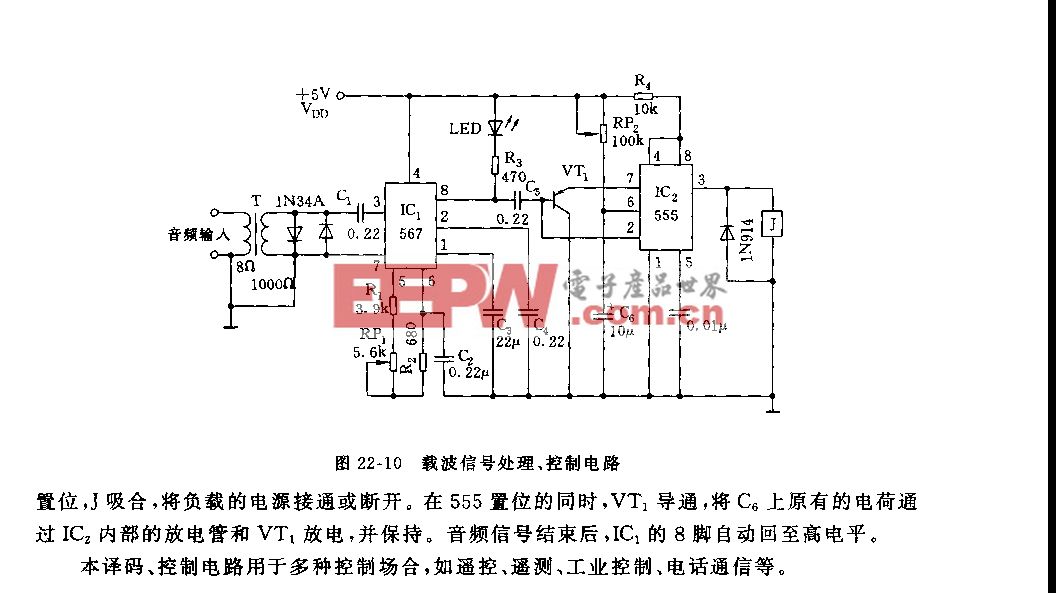

如圖5所示,clk為運算的總控制時鐘;reset為復(fù)位控制信號,高電平有效;rd為讀使能信號,低電平有效;wr為寫使能信號,低電平有效;wr_clk為寫時鐘信號,上升沿觸發(fā);q_clk為讀時鐘信號,上升沿觸發(fā);ab_re(31:O)和ab_im(31:O)為乘法器輸出的實部和虛部。q_t2為矩陣乘累加模塊的同步時鐘信號;clkll,state(3:O),clkl和state(3:0)是狀態(tài)機的控制信號,控制矩陣運算規(guī)則。

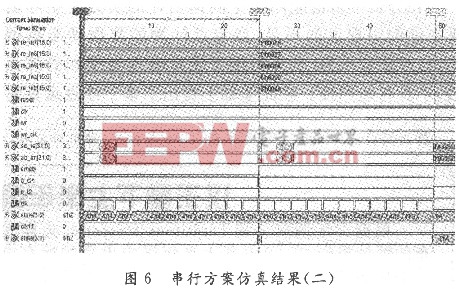

如圖5所示,在100 ns時reset信號有效(即reset=‘1’),所有狀態(tài)清零。從335~635 ns間,寫使能信號有效(wr=‘O’)且有兩個寫時鐘信號的上升沿到來,即向任意一個通道的FIFO中存入兩個快拍采樣數(shù)據(jù),最后輸出結(jié)果應(yīng)該有兩個矩陣,如圖6所示。當(dāng)FIFO為空時,運算停止,所有狀態(tài)清零。等待新采樣數(shù)據(jù)的到來。

圖5中,在350 ns時,讀使能有效(rd=‘0’)且有一個讀時鐘信號的上升沿到來,所以empty信號存在短暫的不空(empty=‘O’)狀態(tài),捕獲到這個信息,便觸發(fā)單穩(wěn)態(tài)觸發(fā)器模塊,產(chǎn)生具有121個clk時鐘周期長度,占空比為120:1的q_clk信號,進行FIFO的讀操作。

在350~535 ns時間段,因為寫時鐘信號沒有到來,所以FIFO為空(empty=‘1’)。從550 ns~24.75 μs時間段讀時鐘信號沒有上升沿到來,整個設(shè)計處于第一個矩陣的運算過程中,即運算一個矩陣所需要的時間為24.2 μs。與此同時,第二個數(shù)據(jù)寫入FIFO,empty一直處于不空狀態(tài)(empty=‘O’)。

在第一個矩陣運算結(jié)束之后,即24.6μs時,系統(tǒng)檢測到empty=‘0’,開始讀數(shù)據(jù)并觸發(fā)第二個矩陣運算的時鐘控制信號。如圖6所示,在24.6μs時,empty=‘1’。FIFO中的第二個數(shù)據(jù)被讀出,處于空狀態(tài)。從24.85~49.05μs進入第二個矩陣的運算周期。

在仿真時,輸人數(shù)據(jù)為16位的定點數(shù)(1+j1;O+jO;2+j2;3+j3;4+j4;5+j5,6+j6;7+j7;8+j8;9+j9;A+jA),輸出結(jié)果為32位的單精度浮點數(shù)。選擇的主時鐘周期為200 ns。在實際調(diào)試過程中,整個系統(tǒng)可以在50 MHz主時鐘頻率下正常工作。

評論