一種基于FPGA的復數浮點協方差矩陣實現

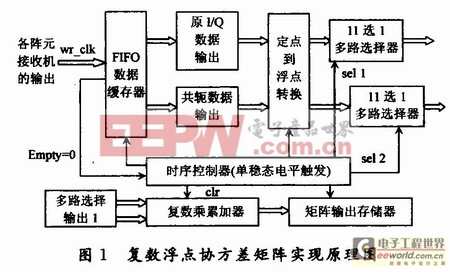

以11陣元的均勻圓陣為例,其協方差矩陣的求解方案原理框圖如圖1所示。

1.1 FIFO數據緩存器

在該設計方案中選擇FIFO作為數據存儲器,這是因為一旦多路接收機有數據輸出,就會啟動FIFO進行存儲,進而FIFO的不空信號有效(empty=O),觸發后續的矩陣運算;否則,運算停止,一切狀態清零,FPGA恢復idle(空閑)狀態,等待新的快拍采樣數據的到來。

這樣可以很方便地控制運算的開始和結束。矩陣運算所需要的同步時鐘需要設計一個類似于單穩態觸發器的模塊。當檢測到empty=‘0’時,就觸發一個含有121個clk(對于串行方案而言)時鐘信號周期長度的高電平。該高電平與主時鐘相與便可以得到運算的同步時鐘。

1.2 數據共軛轉換

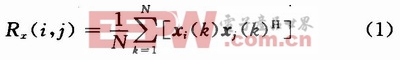

由于測向陣列的輸出矢量X(t)是一個復矢量,對其求協方差矩陣需用陣列輸出列矢量X(t)與其共軛轉置矢量XH(n)對應相乘。如式(1)所示:

1.3 定點數到浮點數的轉換

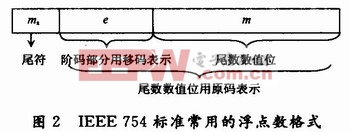

定點計算在硬件上實現簡單,計算速度比浮點計算要快,但是表示操作數的動態范圍受到限制,浮點數計算硬件實現比較困難;一次計算花費的時間也遠大于定點計算的花費,但是其表示的操作數動態范圍大,精度高。在本設計中,考慮到系統的數據動態范圍和運算精度,選擇浮點計算。由于運算數據是直接從接收機I,Q兩路通道的A/D變換器的輸出獲得,為定點數,因此必須要有一個將A/D采樣的定點數據轉換為浮點數的過程。設計中將16位定點數轉換為IEEE 754標準的單精度格式。32位單精度格式如圖2所示,最高位為符號位,其后8位為指數e(用移碼表示,基數f=2,偏移量為127),余下的23位為尾數m。

評論